General-purpose timers (TIM21/22) RM0367

582/1043 RM0367 Rev 7

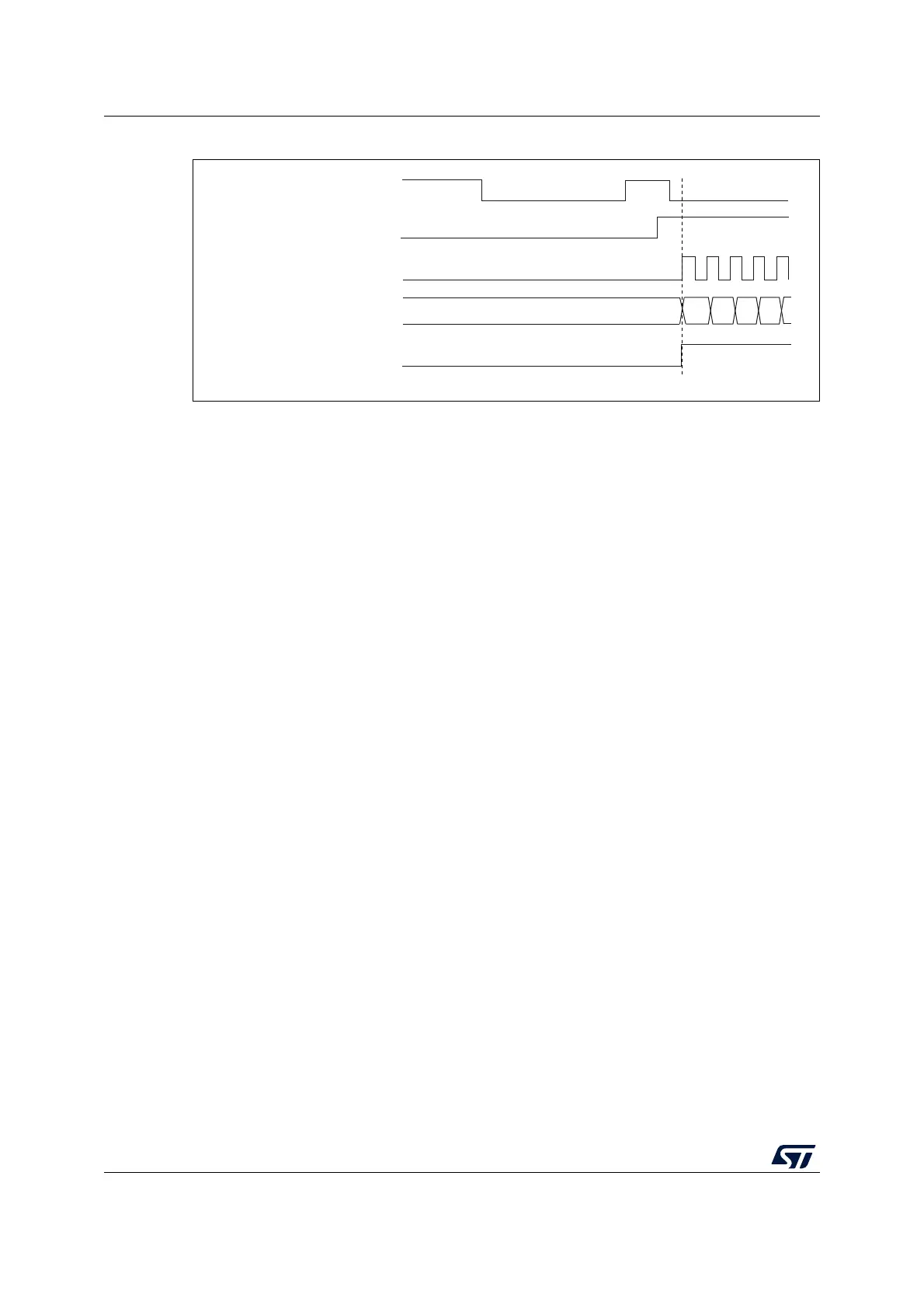

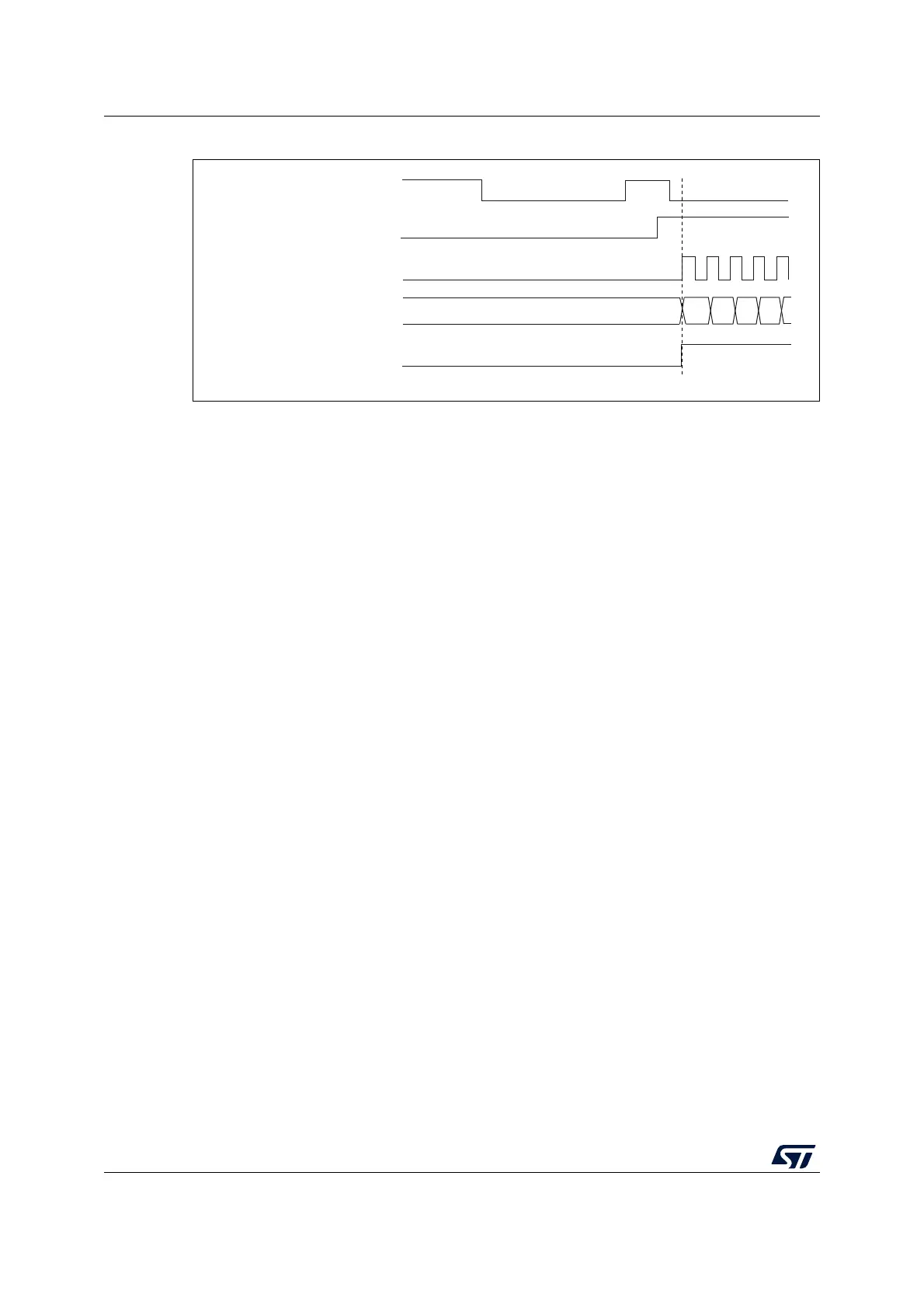

Figure 189. Control circuit in trigger mode

22.3.14 Timer synchronization (TIM21/22)

The timers are linked together internally for timer synchronization or chaining. Refer to

Section 21.3.15: Timer synchronization on page 516 for details.

22.3.15 Debug mode

When the microcontroller enters debug mode (Cortex

®

-M0+ core halted), the TIMx counter

either continues to work normally or stops, depending on DBG_TIMx_STOP configuration

bit in DBG module. For more details, refer to Section 33.9.2: Debug support for timers,

watchdog and I

2

C.

MS31403V1

TI2

cnt_en

37

Counter clock = ck_cnt = ck_psc

Counter register

38

34

35 36

TIF

Loading...

Loading...