General-purpose timers (TIM2/TIM3) RM0367

518/1043 RM0367 Rev 7

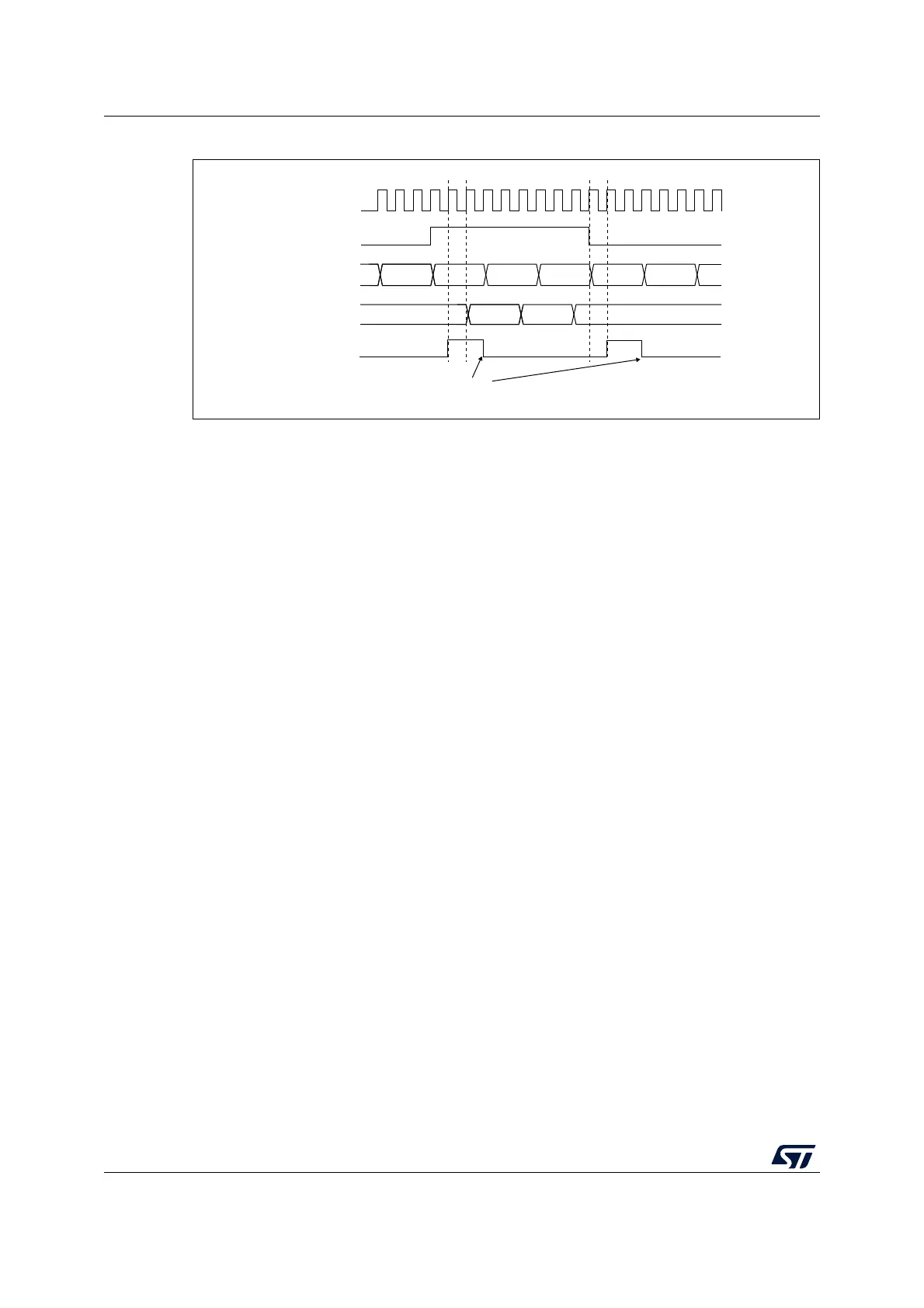

Figure 147. Gating timer y with OC1REF of timer x

In the example in Figure 147, the Timer y counter and prescaler are not initialized before

being started. So they start counting from their current value. It is possible to start from a

given value by resetting both timers before starting Timer x. Then any value can be written

in the timer counters. The timers can easily be reset by software using the UG bit in the

TIMx_EGR registers.

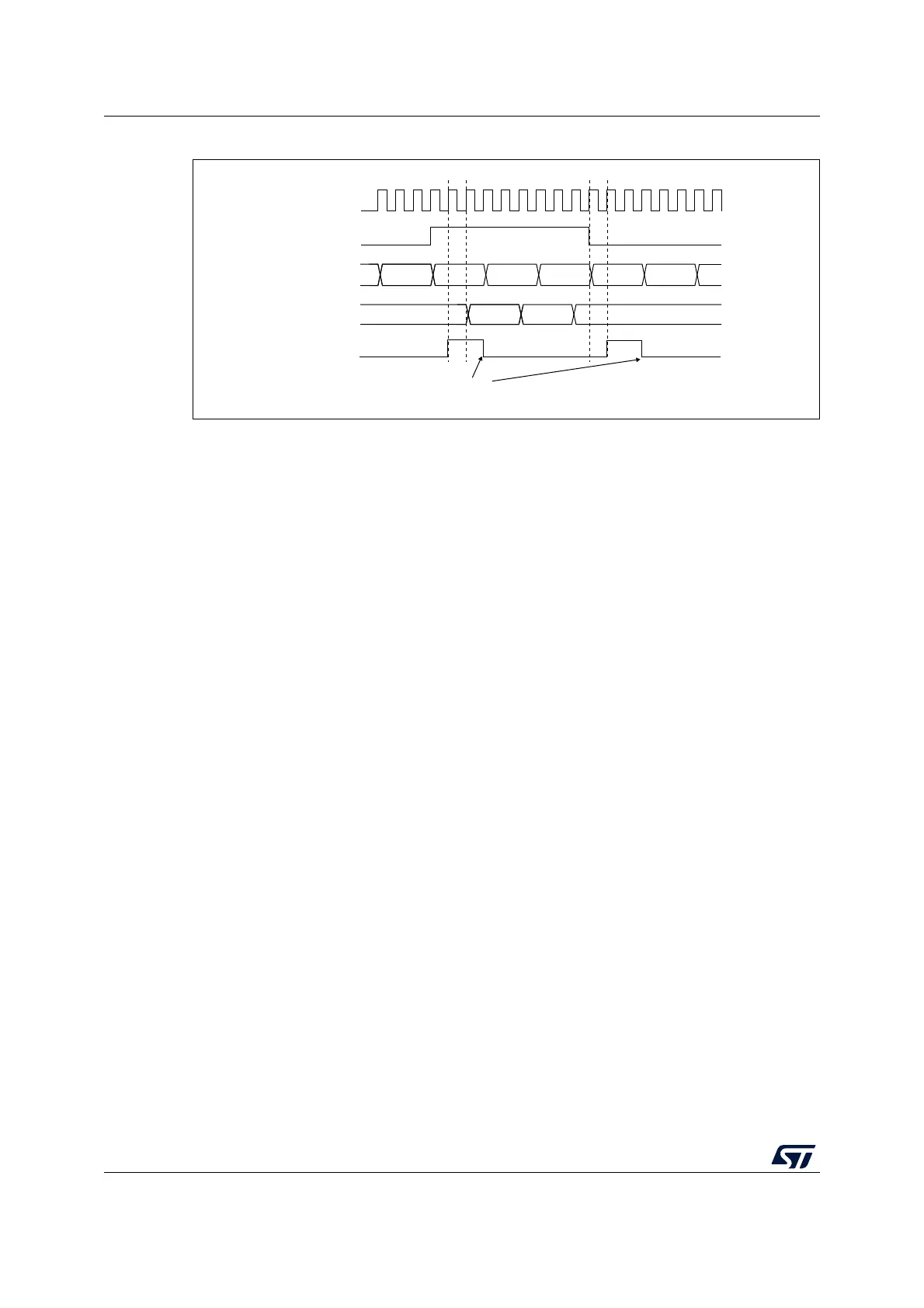

In the next example, we synchronize Timer x and Timer y. Timer x is the master and starts

from 0. Timer y is the slave and starts from 0xE7. The prescaler ratio is the same for both

timers. Timer y stops when Timer x is disabled by writing ‘0 to the CEN bit in the TIMy_CR1

register:

1. Configure Timer x master mode to send its Output Compare 1 Reference (OC1REF)

signal as trigger output (MMS=100 in the TIMx_CR2 register).

2. Configure the Timer x OC1REF waveform (TIMx_CCMR1 register).

3. Configure Timer y to get the input trigger from Timer x (TS=000 in the TIMy_SMCR

register).

4. Configure Timer y in gated mode (SMS=101 in TIMy_SMCR register).

5. Reset Timer x by writing ‘1 in UG bit (TIMx_EGR register).

6. Reset Timer y by writing ‘1 in UG bit (TIMy_EGR register).

7. Initialize Timer y to 0xE7 by writing ‘0xE7’ in the timer y counter (TIMy_CNTL).

8. Enable Timer y by writing ‘1 in the CEN bit (TIMy_CR1 register).

9. Start Timer x by writing ‘1 in the CEN bit (TIMx_CR1 register).

10. Stop Timer x by writing ‘0 in the CEN bit (TIMx_CR1 register).

For code example, refer to A.11.19: Master and slave synchronization code example.

MS33137V1

CK_INT

FC FD

FE FF 00 01

TIMERx-OC1REF

TIMERx-CNT

30463045

3047

3048

TIMERy-CNT

TIMERy-TIF

Write TIF = 0

Loading...

Loading...