RM0367 Rev 7 351/1043

RM0367 Analog-to-digital converter (ADC)

352

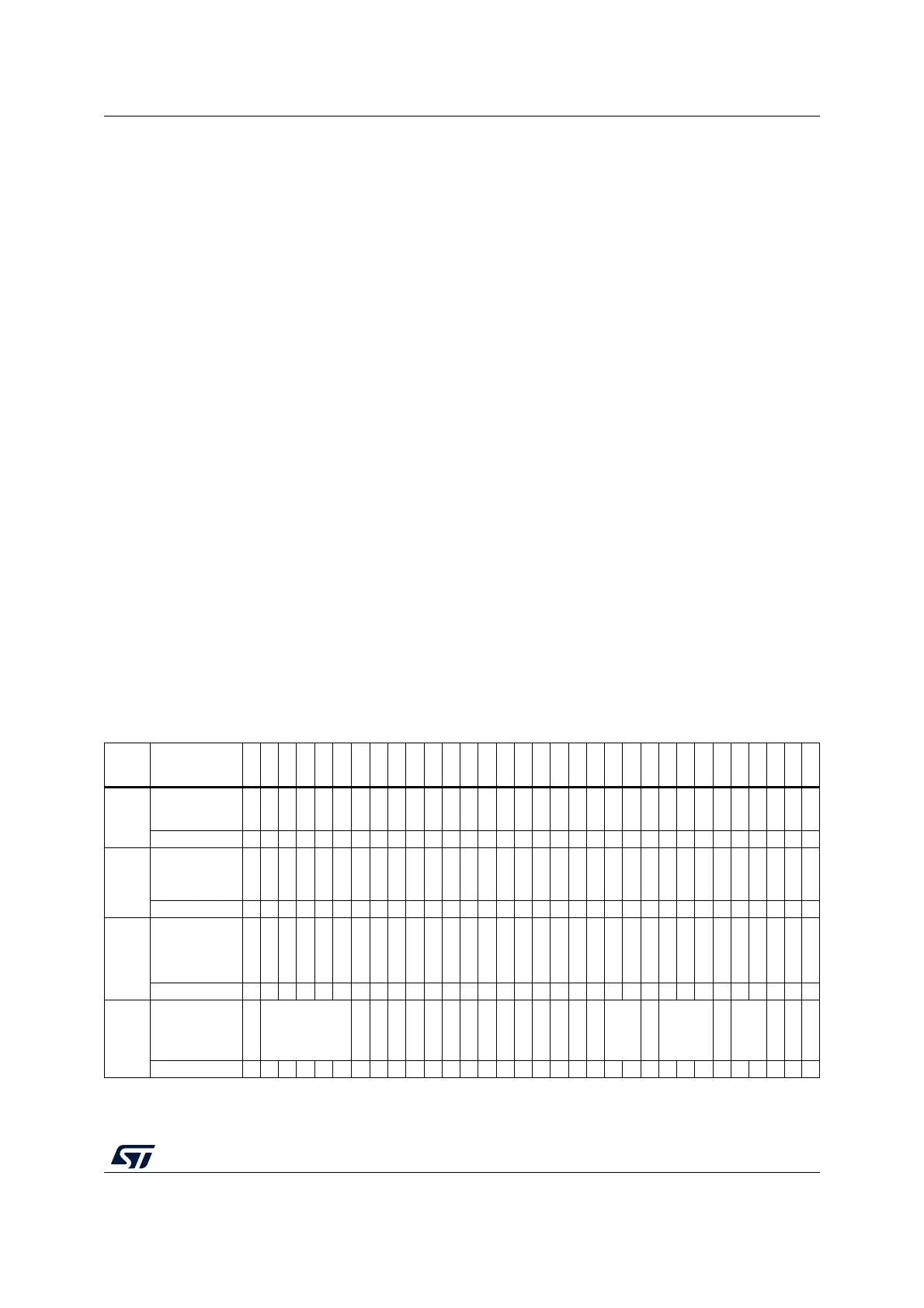

14.13 ADC register map

The following table summarizes the ADC registers.

Bit 22 VREFEN: V

REFINT

enable

This bit is set and cleared by software to enable/disable the V

REFINT

.

0: V

REFINT

disabled

1: V

REFINT

enabled

Note: Software is allowed to write this bit only when ADSTART = 0 (which ensures that no conversion

is ongoing).

Bits 21:18 PRESC[3:0]: ADC prescaler

Set and cleared by software to select the frequency of the clock to the ADC. The clock is common for

all the ADCs.

0000: input ADC clock not divided

0001: input ADC clock divided by 2

0010: input ADC clock divided by 4

0011: input ADC clock divided by 6

0100: input ADC clock divided by 8

0101: input ADC clock divided by 10

0110: input ADC clock divided by 12

0111: input ADC clock divided by 16

1000: input ADC clock divided by 32

1001: input ADC clock divided by 64

1010: input ADC clock divided by 128

1011: input ADC clock divided by 256

Other: Reserved

Note: Software is allowed to write these bits only when the ADC is disabled (ADCAL = 0,

ADSTART = 0, ADSTP = 0, ADDIS = 0 and ADEN = 0).

Bits 17:0 Reserved, must be kept at reset value.

Table 68. ADC register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

ADC_ISR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

EOCAL

Res.

Res.

Res.

AWD

Res.

Res.

OVR

EOS

EOC

EOSMP

ADRDY

Reset value

0 0 00000

0x04

ADC_IER

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

EOCALIE

Res.

Res.

Res.

AWDIE

Res.

Res.

OVRIE

EOSIE

EOCIE

EOSMPIE

ADRDYIE

Reset value

0 0 00000

0x08

ADC_CR

ADCAL

Res.

Res.

ADVREGEN

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

ADSTP

Res.

ADSTART

ADDIS

ADEN

Reset value 0

0 0 000

0x0C

ADC_CFGR1

Res.

AWDCH[4:0]

Res.

Res.

AWDEN

AWDSGL

Res.

Res.

Res.

Res.

Res.

DISCEN

AUTOFF

WAIT

CONT

OVRMOD

EXTEN[1:0]

Res.

EXTSEL

[2:0]

ALIGN

RES

[1:0]

SCANDIR

DMACFG

DMAEN

Reset value

00000 00

0000000 000000000

Loading...

Loading...