Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0367

806/1043 RM0367 Rev 7

Let us take this example: OVER8 = 0, M bits = 10, ONEBIT = 1, BRR [3:0] = 0000.

In these conditions, according to Table 142: Tolerance of the USART receiver when BRR

[3:0] = 0000, the USART receiver tolerance is 4.86 %.

DTRA + DQUANT + DREC + DTCL + DWU < USART receiver's tolerance

DWU max = t

WUUSART

/ (9 x Tbit Min)

Tbit Min = t

WUUSART

/ (9 x DWU max)

If we consider an ideal case where the parameters DTRA, DQUANT, DREC and DTCL are

at 0%, the DWU max is 4.86 %. In reality, we need to consider at least the HSI inaccuracy.

Let us consider HSI inaccuracy = 1 %, t

WUUSART

= 8.1 μs (in case of Stop mode with main

regulator in Run mode, Range 1 ):

DWU max = 4.86 % - 1 % = 3.86 %

Tbit min = 8.1 µs / (9 ₓ 3.86 %) = 23.31 μs.

In these conditions, the maximum baud rate allowing to wakeup correctly from Stop mode is

1/23.31 μs = 42 kbaud.

29.6 USART in low-power modes

29.7 USART interrupts

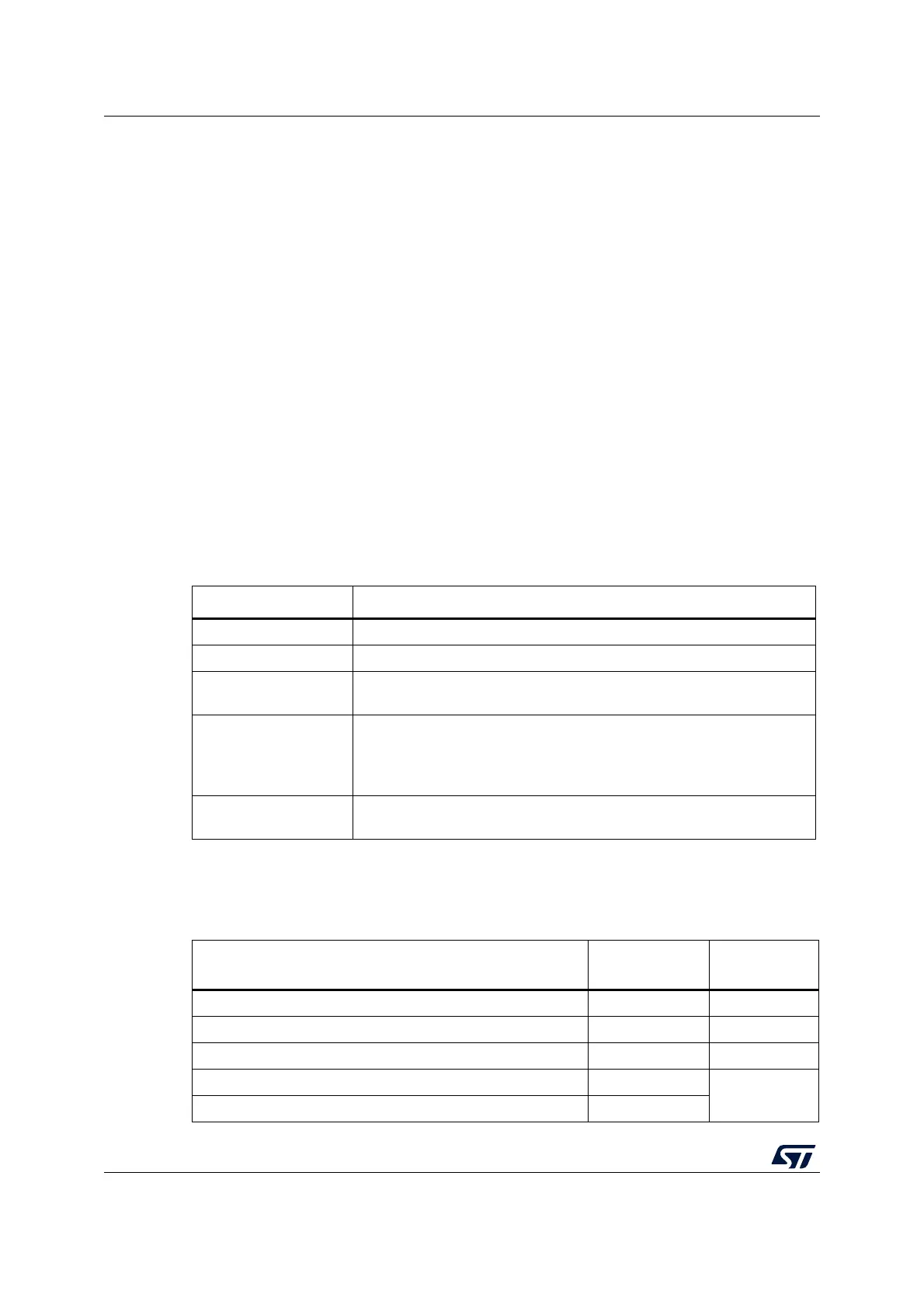

Table 145. Effect of low-power modes on the USART

Mode Description

Sleep No effect. USART interrupt causes the device to exit Sleep mode.

Low-power run No effect.

Low-power sleep

No effect. USART interrupt causes the device to exit Low-power sleep

mode.

Stop

The USART is able to wake up the MCU from Stop mode when the UESM

bit is set and the USART clock is set to HSI16 or LSE.

The MCU wakeup from Stop mode can be done using the standard RXNE

interrupt.

Standby

The USART is powered down and must be reinitialized when the device

has exited from Standby mode.

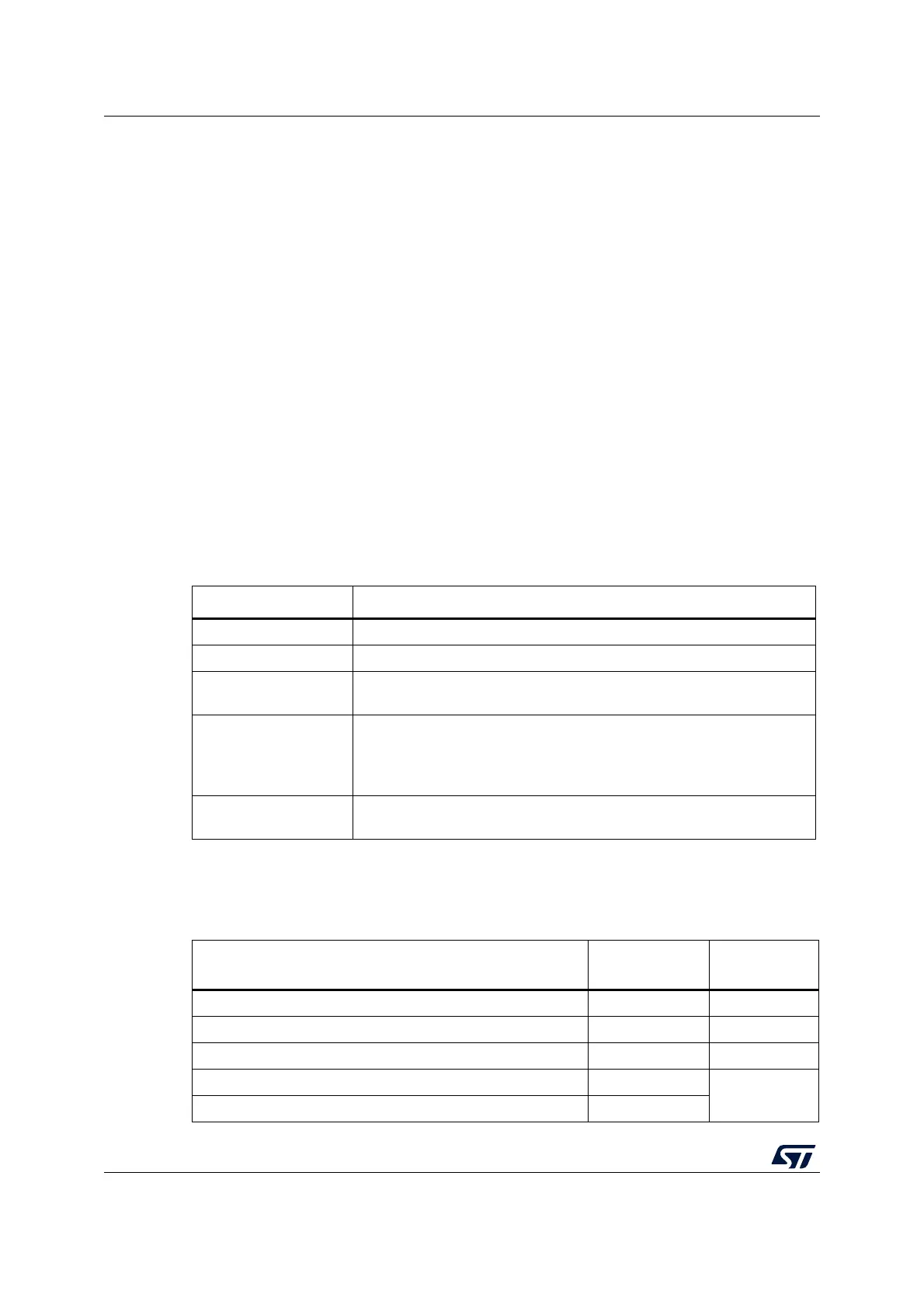

Table 146. USART interrupt requests

Interrupt event Event flag

Enable Control

bit

Transmit data register empty TXE TXEIE

CTS interrupt CTSIF CTSIE

Transmission Complete TC TCIE

Receive data register not empty (data ready to be read) RXNE

RXNEIE

Overrun error detected ORE

Loading...

Loading...