Reset and clock control (RCC) RM0367

204/1043 RM0367 Rev 7

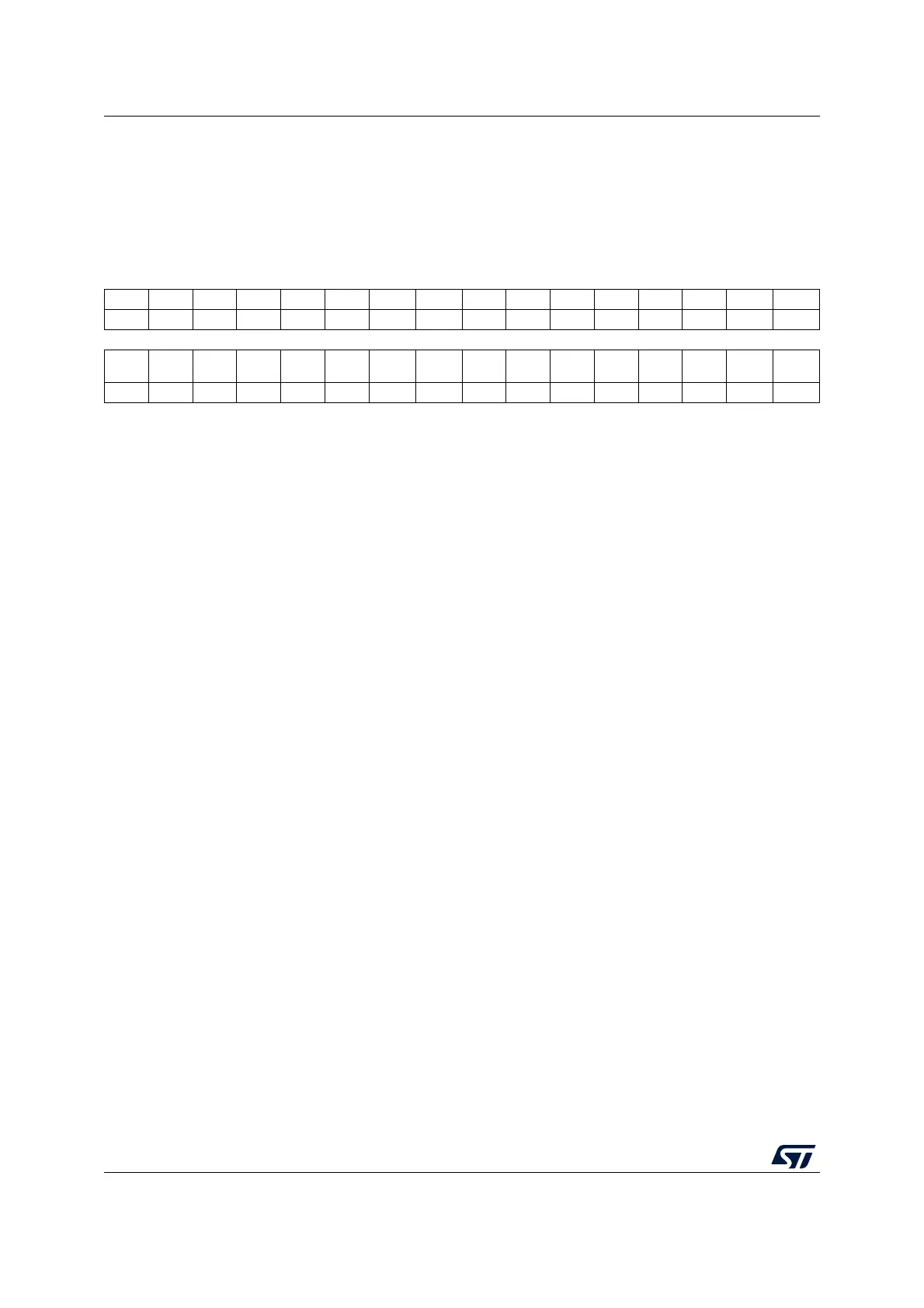

7.3.12 GPIO clock enable register (RCC_IOPENR)

Address: 0x2C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res.

IOPH

EN

Res. Res.

IOPE

EN

IOPD

EN

IOPC

EN

IOPB

EN

IOPA

EN

rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 IOPHEN: I/O port H clock enable bit

This bit is set and cleared by software.

0: port H clock disabled

1: port H clock enabled

Bits 6:45 Reserved, must be kept at reset value.

Bit 4 IOPEEN: I/O port E clock enable bit

This bit is set and cleared by software.

0: port E clock disabled

1: port E clock enabled

Bit 3 IOPDEN: I/O port D clock enable bit

This bit is set and cleared by software.

0: port D clock disabled

1: port D clock enabled

Bit 2 IOPCEN: IO port C clock enable bit

This bit is set and cleared by software.

0: port C clock disabled

1: port C clock enabled

Bit 1 IOPBEN: IO port B clock enable bit

This bit is set and cleared by software.

0: port B clock disabled

1: port B clock enabled

Bit 0 IOPAEN: IO port A clock enable bit

This bit is set and cleared by software.

0: port A clock disabled

1: port A clock enabled

Loading...

Loading...