RM0367 Rev 7 219/1043

RM0367 Reset and clock control (RCC)

225

7.3.21 Control/status register (RCC_CSR)

Address: 0x50

Power-on reset value: 0x0C00 0000

Access: 0

≤ wait state ≤ 3, word, half-word and byte access

Wait states are inserted in case of successive accesses to this register.

Note: The LSEON, LSEBYP, RTCSEL,LSEDRV and RTCEN bits in the RCC control and status

register (RCC_CSR) are in the RTC domain. As these bits are write protected after reset,

the DBP bit in the Power control register (PWR_CR) has to be set to be able to modify them.

Refer to Section 6.1.3: RTC and RTC backup registers for further information. These bits

are only reset after a RTC domain reset (see Section 6.1.3). Any internal or external reset

does not have any effect on them.

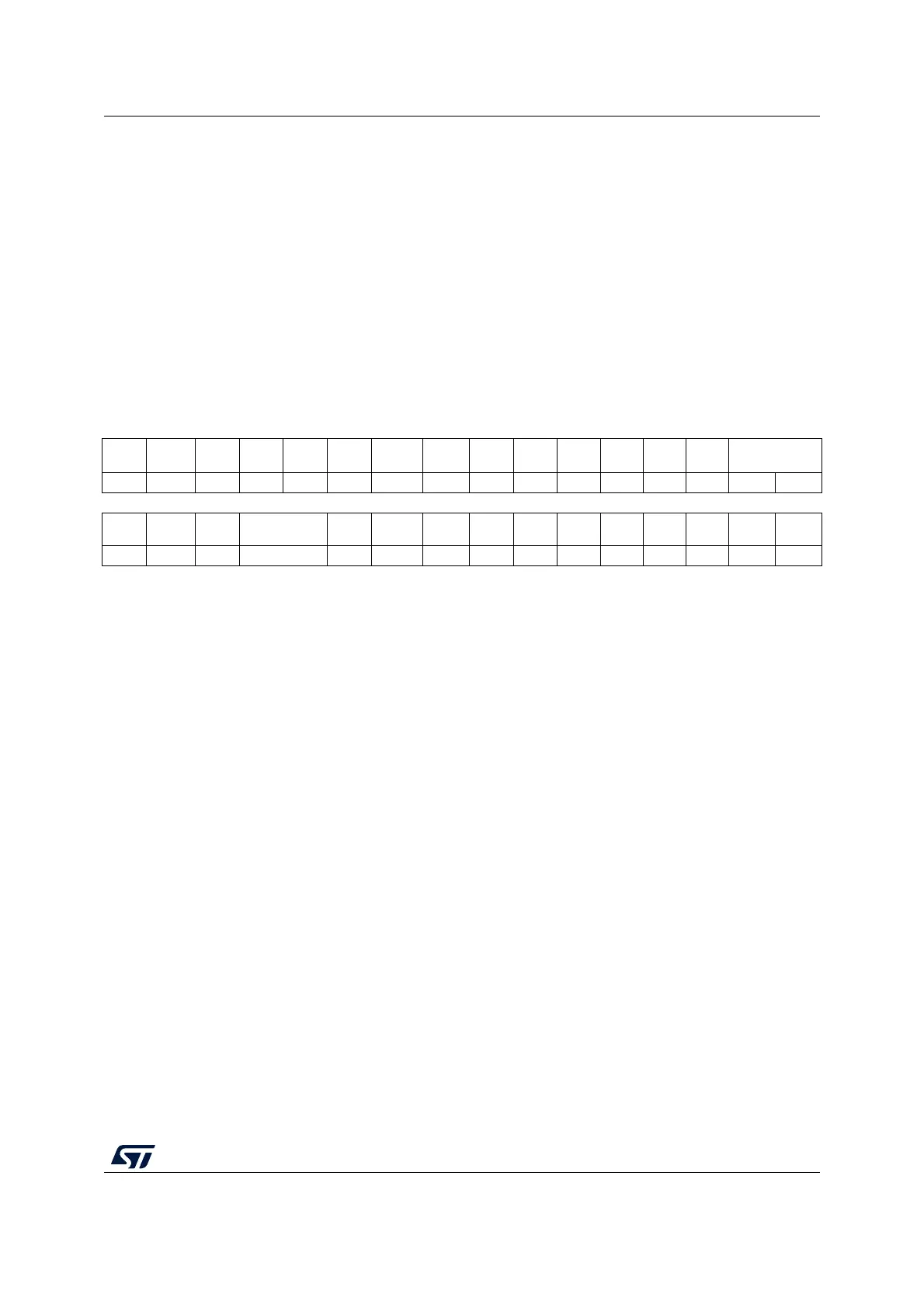

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LPWR

RSTF

WWDG

RSTF

IWDG

RSTF

SFT

RSTF

POR

RSTF

PIN

RSTF

OBL

RS TF

FW

RSTF

RMVF Res. Res. Res.

RTC

RST.

RTC

EN

RTCSEL[1:0]

r r rrrr r rrt_w rwrwrwrw

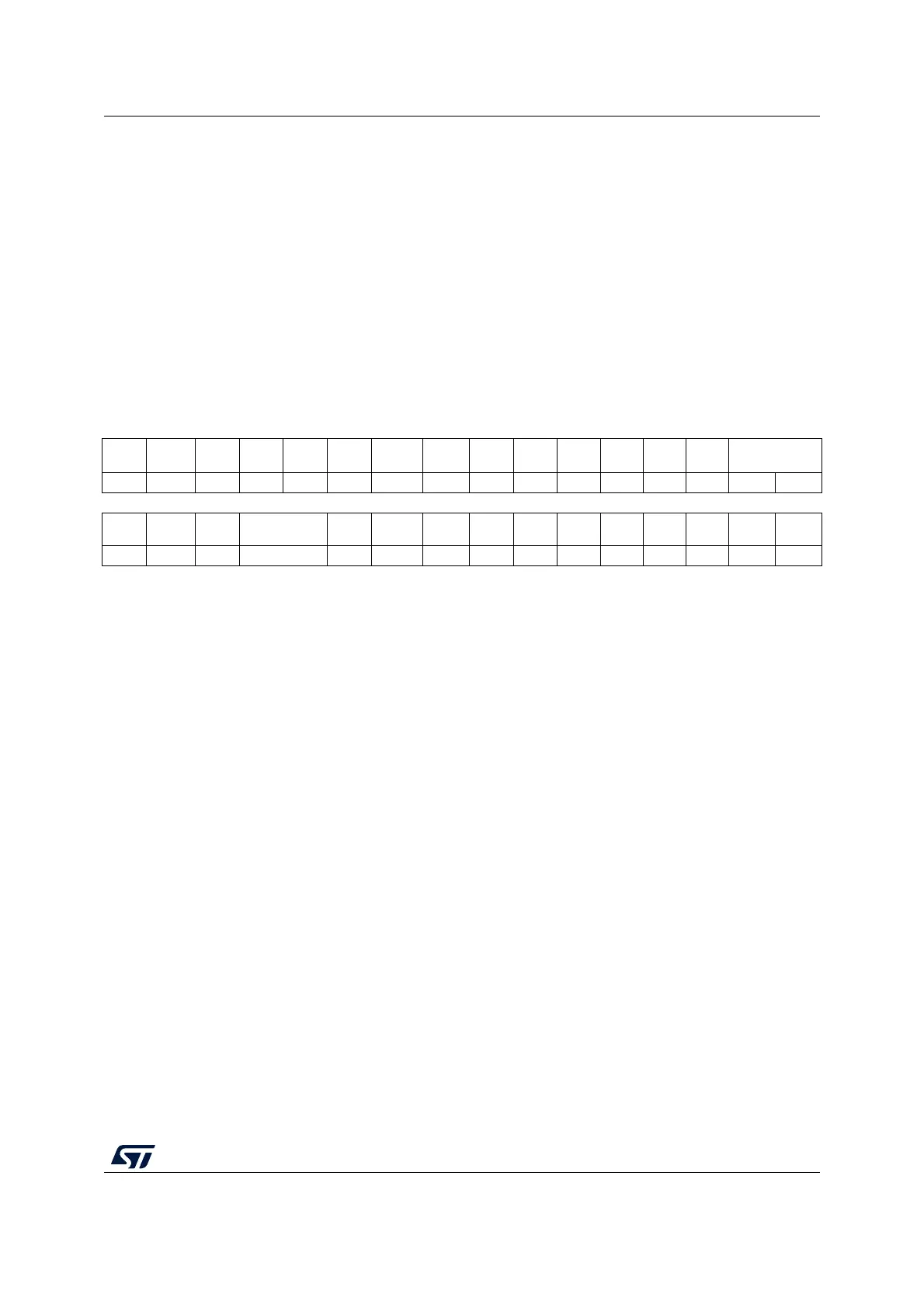

151413121110 9 8 7 65432 1 0

Res.

CSSLS

ED

CSSLS

EON

LSEDRV[1:0]

LSE

BYP

LSERDY LSEON Res. Res. Res. Res. Res. Res.

LSI

RDY

LSION

rrw rw rw r rw rrw

Bit 31 LPWRRSTF: Low-power reset flag

This bit is set by hardware when a Low-power management reset occurs.

It is cleared by writing to the RMVF bit, or by a POR.

0: No Low-power management reset occurred

1: Low-power management reset occurred

For further information on Low-power management reset, refer to Section : Low-power

management reset.

Bit 30 WWDGRSTF: Window watchdog reset flag

This bit is set by hardware when a window watchdog reset occurs.

It is cleared by writing to the RMVF bit, or by a POR.

0: No window watchdog reset occurred

1: Window watchdog reset occurred

Bit 29 IWDGRSTF: Independent watchdog reset flag

This bit is set by hardware when an independent watchdog reset from V

DD

domain occurs.

It is cleared by writing to the RMVF bit, or by a POR.

0: No watchdog reset occurred

1: Watchdog reset occurred

Bit 28 SFTRSTF: Software reset flag

This bit is set by hardware when a software reset occurs.

It is cleared by writing to the RMVF bit, or by a POR.

0: No software reset occurred

1: Software reset occurred

Bit 27 PORRSTF: POR/PDR reset flag

This bit is set by hardware when a POR/PDR reset occurs.

It is cleared by writing to the RMVF bit.

0: No POR/PDR reset occurred

1: POR/PDR reset occurred

Loading...

Loading...