RM0367 Rev 7 687/1043

RM0367 Real-time clock (RTC)

694

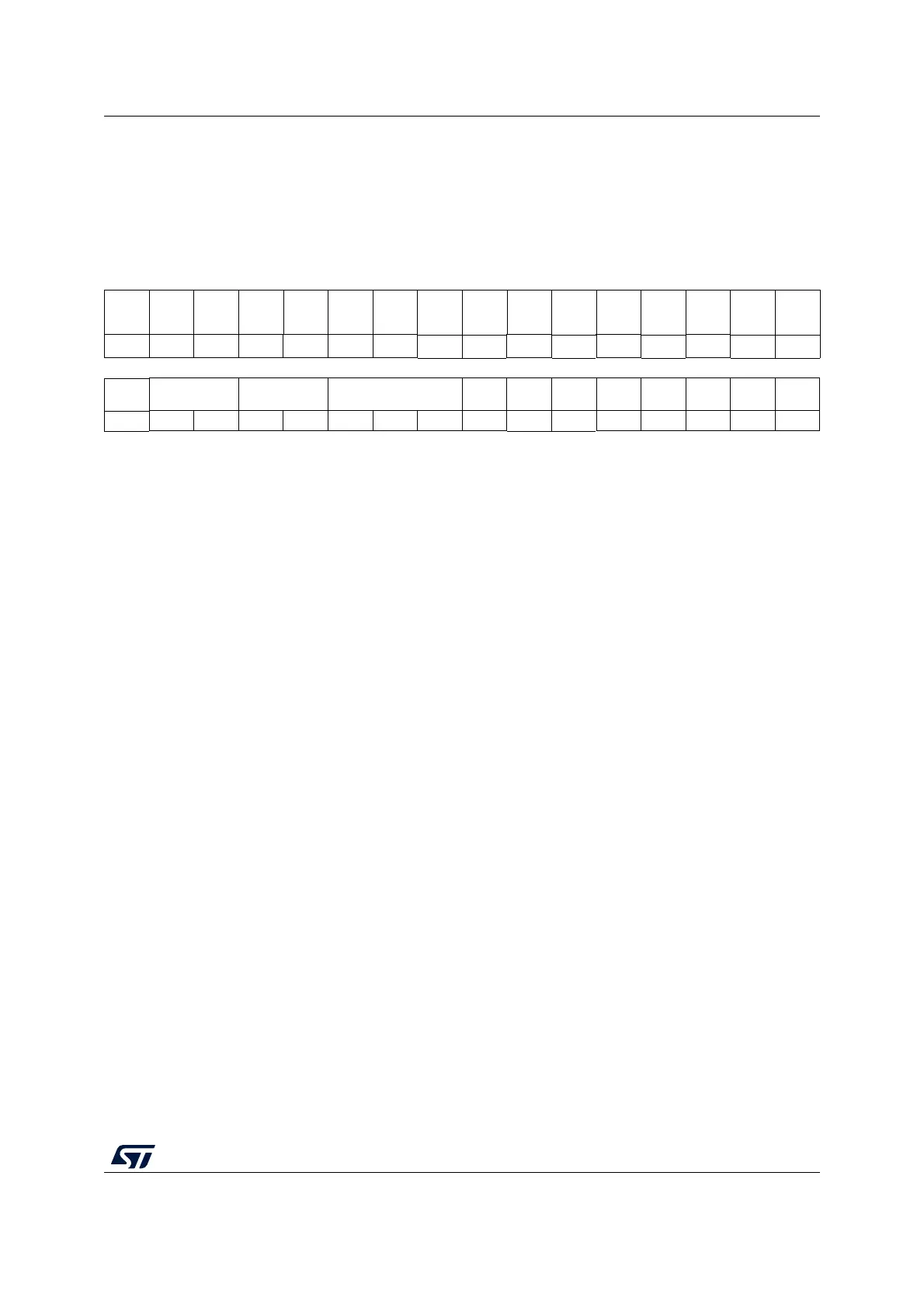

27.7.16 RTC tamper configuration register (RTC_TAMPCR)

Address offset: 0x40

RTC domain reset value: 0x0000 0000

System reset: not affected

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res.

TAMP3

MF

TAMP3

NO

ERASE

TAMP3

IE

TAMP2

MF

TAMP2

NO

ERASE

TAMP2

IE

TAMP1

MF

TAMP1

NO

ERASE

TAMP1

IE

rw rw rw rw rw rw rw rw rw

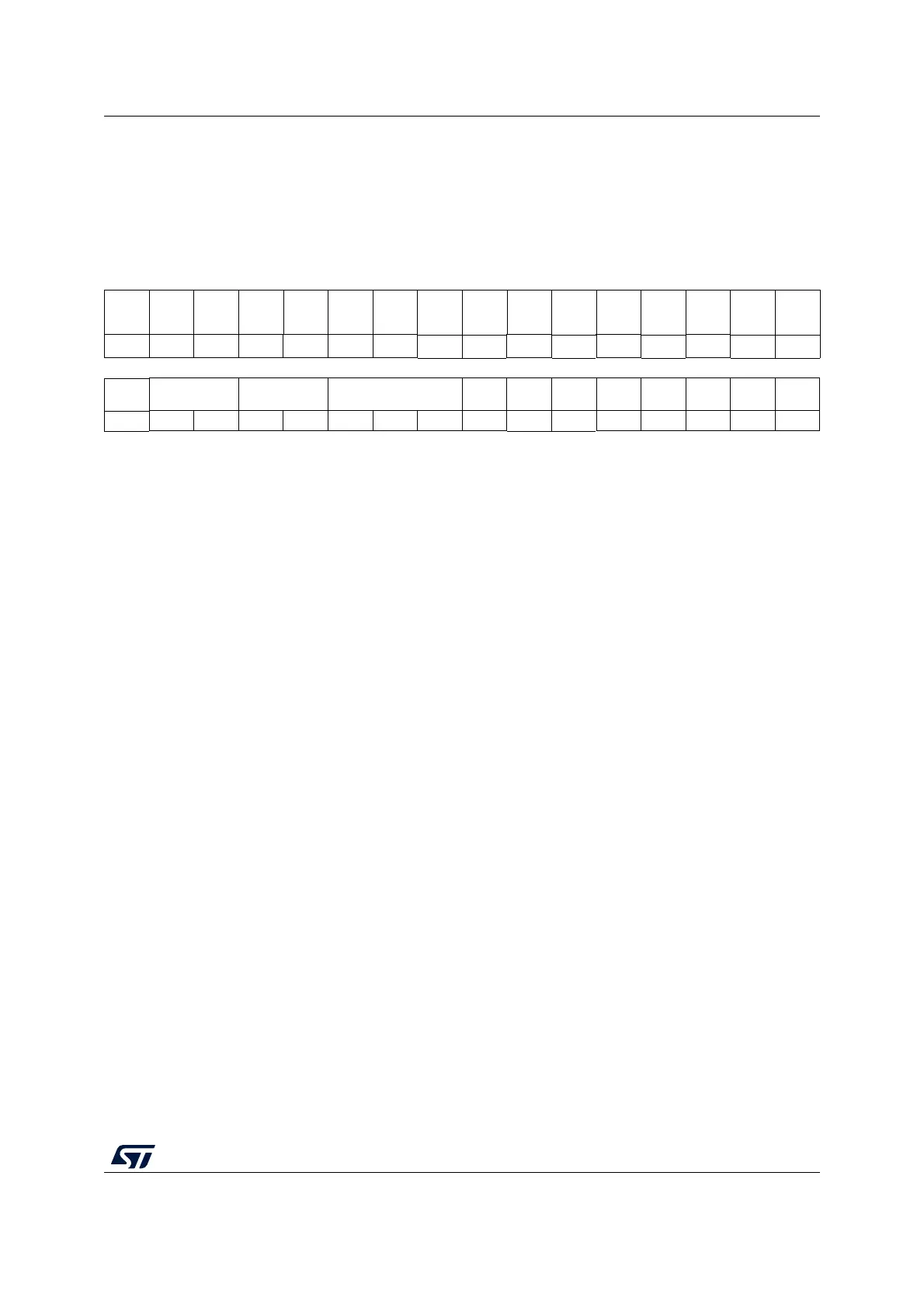

1514131211109876543210

TAMP

PUDIS

TAMPPRCH

[1:0]

TAMPFLT[1:0] TAMPFREQ[2:0]

TAMP

TS

TAMP3

TRG

TAMP3

E

TAMP2

TRG

TAMP2

E

TAMPI

E

TAMP1

TRG

TAMP1

E

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:25 Reserved, must be kept at reset value.

Bit 24 TAMP3MF: Tamper 3 mask flag

0: Tamper 3 event generates a trigger event and TAMP3F must be cleared by software to

allow next tamper event detection.

1: Tamper 3 event generates a trigger event. TAMP3F is masked and internally cleared by

hardware. The backup registers are not erased.

Note: The Tamper 3 interrupt must not be enabled when TAMP3MF is set.

Bit 23 TAMP3NOERASE: Tamper 3 no erase

0: Tamper 3 event erases the backup registers.

1: Tamper 3 event does not erase the backup registers.

Bit 22 TAMP3IE: Tamper 3 interrupt enable

0: Tamper 3 interrupt is disabled if TAMPIE = 0.

1: Tamper 3 interrupt enabled.

Bit 21 TAMP2MF: Tamper 2 mask flag

0: Tamper 2 event generates a trigger event and TAMP2F must be cleared by software to

allow next tamper event detection.

1: Tamper 2 event generates a trigger event. TAMP2F is masked and internally cleared by

hardware. The backup registers are not erased.

Note: The Tamper 2 interrupt must not be enabled when TAMP2MF is set.

Bit 20 TAMP2NOERASE: Tamper 2 no erase

0: Tamper 2 event erases the backup registers.

1: Tamper 2 event does not erase the backup registers.

Bit 19 TAMP2IE: Tamper 2 interrupt enable

0: Tamper 2 interrupt is disabled if TAMPIE = 0.

1: Tamper 2 interrupt enabled.

Bit 18 TAMP1MF: Tamper 1 mask flag

0: Tamper 1 event generates a trigger event and TAMP1F must be cleared by software to

allow next tamper event detection.

1: Tamper 1 event generates a trigger event. TAMP1F is masked and internally cleared by

hardware.The backup registers are not erased.

Note: The Tamper 1 interrupt must not be enabled when TAMP1MF is set.

Loading...

Loading...