Debug support (DBG) RM0367

960/1043 RM0367 Rev 7

Refer to the Cortex

®

-M0+ TRM for a detailed description of DPACC and APACC registers.

The packet request is always followed by the turnaround time (default 1 bit) where neither

the host nor target drive the line.

The ACK Response must be followed by a turnaround time only if it is a READ transaction

or if a WAIT or FAULT acknowledge has been received.

The DATA transfer must be followed by a turnaround time only if it is a READ transaction.

33.5.3 SW-DP state machine (reset, idle states, ID code)

The State Machine of the SW-DP has an internal ID code which identifies the SW-DP. It

follows the JEP-106 standard. This ID code is the default Arm

®

one and is set to

0x0BC11477(corresponding to Cortex

®

-M0+).

Note: Note that the SW-DP state machine is inactive until the target reads this ID code.

• The SW-DP state machine is in RESET STATE either after power-on reset, or after the

line is high for more than 50 cycles

• The SW-DP state machine is in IDLE STATE if the line is low for at least two cycles

after RESET state.

• After RESET state, it is mandatory to first enter into an IDLE state AND to perform a

READ access of the DP-SW ID CODE register. Otherwise, the target will issue a

FAULT acknowledge response on another transactions.

Further details of the SW-DP state machine can be found in the Cortex

®

-M0+ TRM and the

CoreSight Design Kit r1p0 TRM.

5 Parity Single bit parity of preceding bits

6Stop 0

7Park

Not driven by the host. Must be read as “1” by the target

because of the pull-up

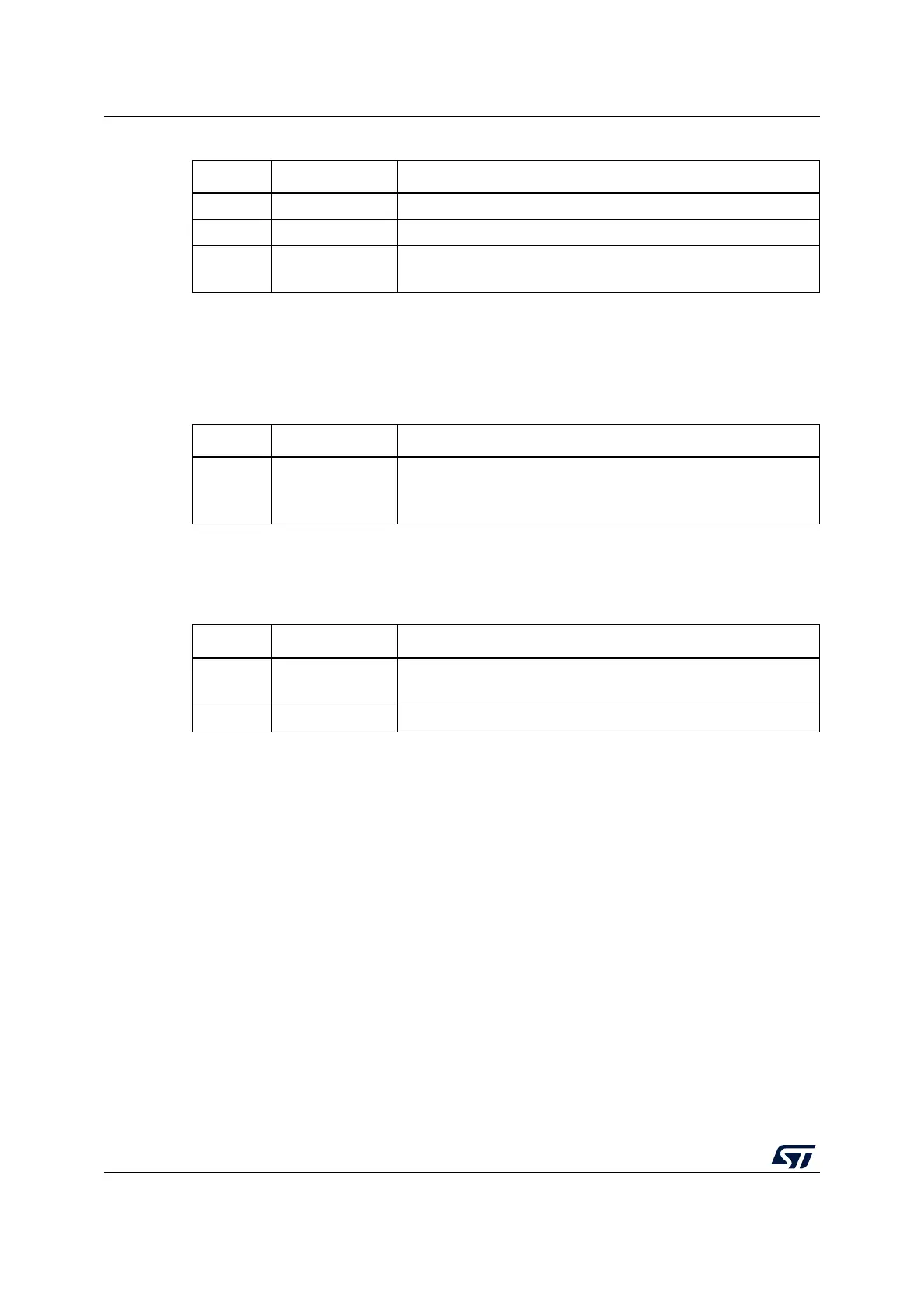

Table 175. ACK response (3 bits)

Bit Name Description

0..2

ACK

001: FAULT

010: WAIT

100: OK

Table 176. DATA transfer (33 bits)

Bit Name Description

0..31

WDATA or

RDATA

Write or Read data

32

Parity

Single parity of the 32 data bits

Table 174. Packet request (8-bits) (continued)

Bit Name Description

Loading...

Loading...