General-purpose timers (TIM2/TIM3) RM0367

490/1043 RM0367 Rev 7

DMA request is sent). This is to avoid generating both update and capture interrupt when

clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in

TIMx_SR register) is set (depending on the URS bit):

• The buffer of the prescaler is reloaded with the preload value (content of the TIMx_PSC

register).

• The auto-reload active register is updated with the preload value (content of the

TIMx_ARR register). Note that if the update source is a counter overflow, the auto-

reload is updated before the counter is reloaded, so that the next period is the expected

one (the counter is loaded with the new value).

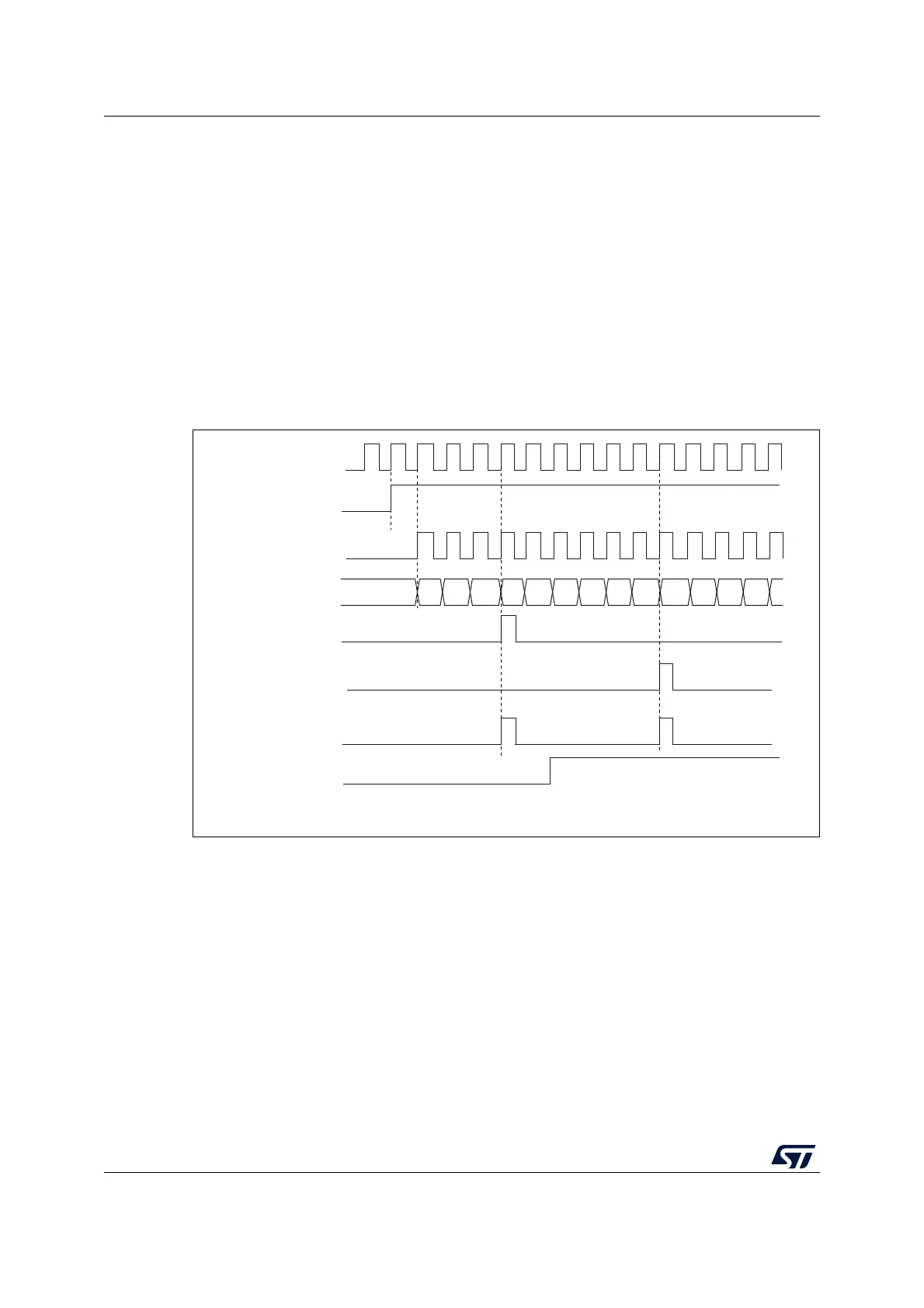

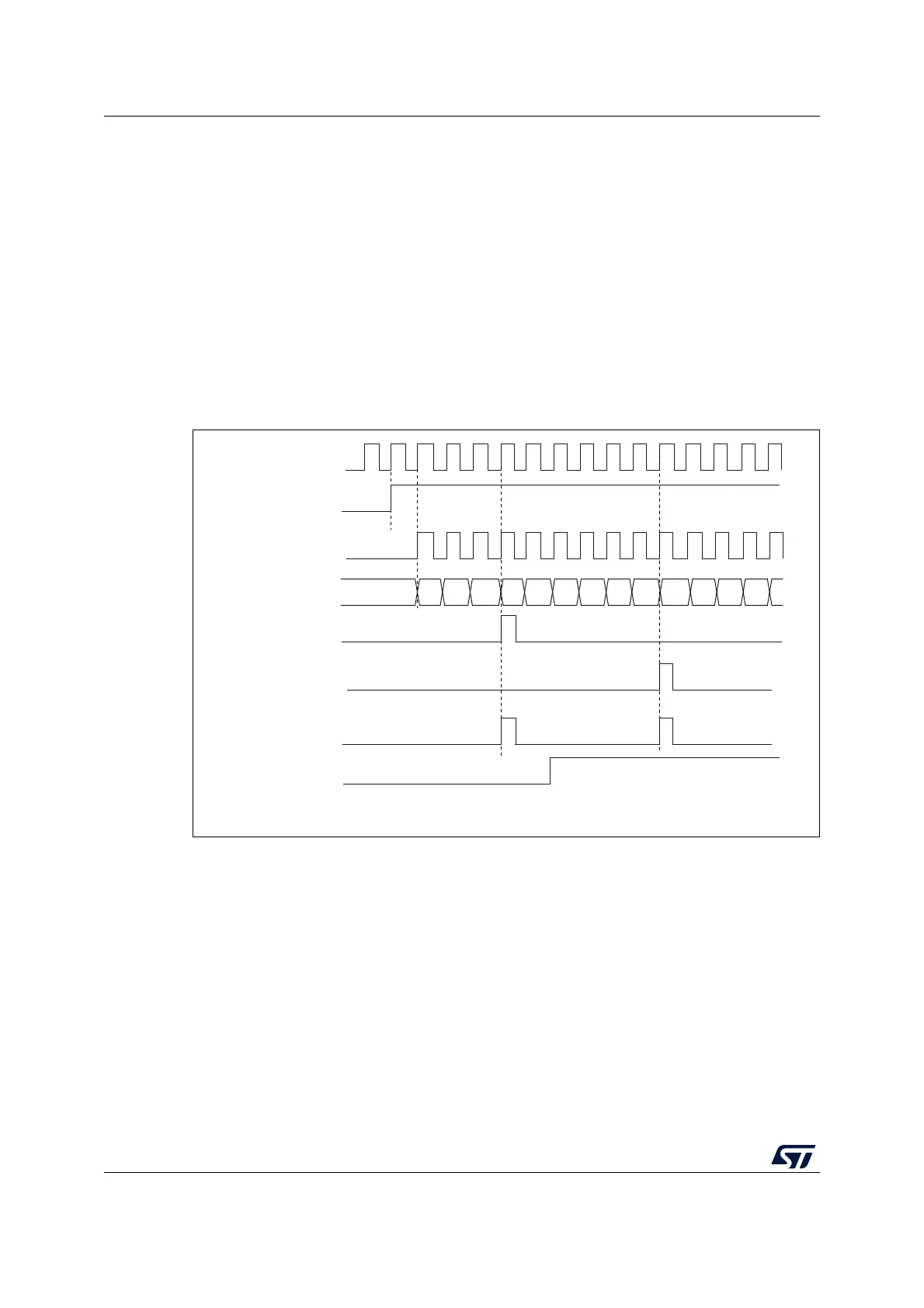

The following figures show some examples of the counter behavior for different clock

frequencies.

Figure 120. Counter timing diagram, internal clock divided by 1, TIMx_ARR=0x6

1. Here, center-aligned mode 1 is used (for more details refer to Section 21.4.1: TIMx control register 1

(TIMx_CR1) on page 523).

MS31189V1

CK_PSC

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag

(UIF)

00020304

05

06

01

CEN

02 03 0401 05 0304

Counter underflow

Loading...

Loading...