RM0367 Rev 7 77/1043

RM0367 Flash program memory and data EEPROM (FLASH)

122

To manage the fetch, the memory interface uses 4 buffers: at reset (DISAB_BUF = 0,

PRFTEN = 0, PRE_READ = 0). 3 buffers are used to manage the jumps and 1 buffer to

store the last value fetched. With this configuration, the 4 buffers for fetch are organized in 2

groups with separate histories: the group for loops and the group for the last value fetched.

Setting the PRFTEN bit to 1 enables the prefetch. The prefetch is a speculative read in the

NVM, which is executed when no read is requested by masters, and where the memory

interface reads from the last address fetched increased by 4 (one word). This read is with a

lower priority and it is aborted if a master requests a read (data or fetch) to a different

address than the prefetch one. When the prefetch is enabled, one buffer for loops is moved

to a new group (of only one buffer) to store the prefetched value: 2 buffers continue to store

the jumps, 1 buffer is used for prefetch and 1 buffer is used for the last value.

The memory interface can only prefetch one address, so the function is temporarily disabled

when no fetch is done and the prefetch is already completed. After a prefetch, if the master

requests the prefetched value, the content of the prefetch buffer is copied to the last value

buffer and a new prefetch is enabled. If, instead, the master requests a different address,

the content of the prefetch buffer is lost, a read in the NVM is started (if necessary) and,

when it is complete, a new prefetch is enabled at the new address fetched increased by 4.

The prefetch can only increase the performance when reading with 1 wait state and for

mostly linear codes: the user must evaluate the pros and cons to enable or not the prefetch

in every situation. The prefetch increases the consumption because many more readings

are done in the NVM (and not all of them will be used by the master). To see the advantages

of prefetch on Dhrystone code, refer to the Dhrystone performances section.

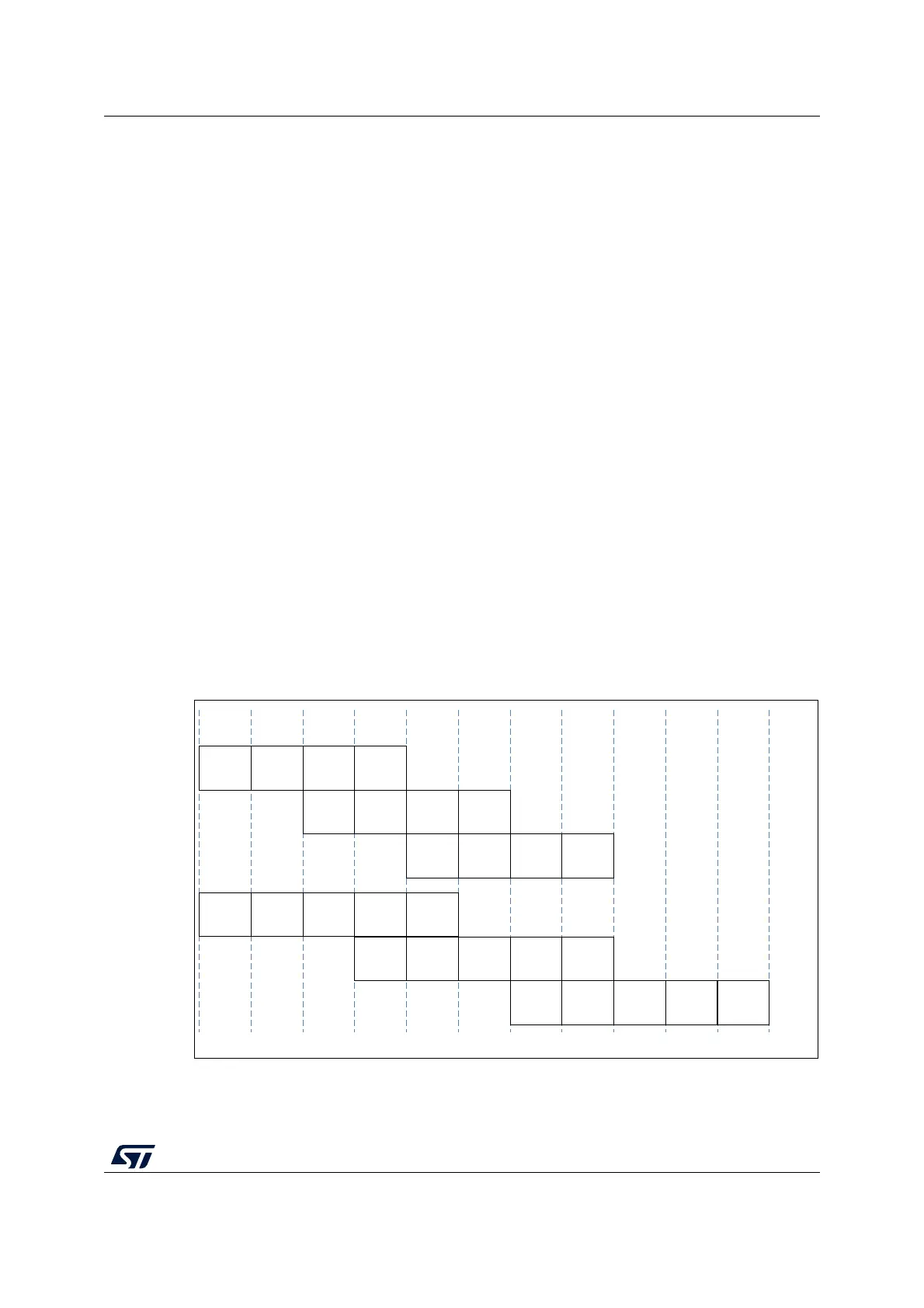

Figure 4 shows the timing to fetch a linear code in the NVM when the prefetch is disabled,

both for 0 wait state (a) and 1 wait state (b). You can compare these two sequences with the

ones in Figure 5, when the prefetch is enabled, to have an idea of the advantages of a

prefetch on a linear code with 0 and 1 wait states.

Figure 4. Timing to fetch and execute instructions with prefetch disabled

1. (a) corresponds to 0 wait state.

2. (b) corresponds to 1 wait state.

MS32396V1

cycle

1

cycle

2

cycle

3

cycle

4

cycle

6

cycle

7

cycle

8

cycle

9

cycle

10 11

cycle

5

Fetch

1 & 2

Addr

1 & 2

Exec.

1

Exec.

2

Fetch

3 & 4

Addr

3 & 4

Exec.

3

Exec.

4

Fetch

5 & 6

Addr

5 & 6

Exec.

5

Exec.

6

(a)

Fetch

1 & 2

Addr

1 & 2

Exec.

1

Wait

Exec.

2

Fetch

3 & 4

Addr

3 & 4

Exec.

3

Wait

Exec.

4

Fetch

5 & 6

Addr

5 & 6

Exec.

5

Wait

Exec.

6

(b)

cycle

Loading...

Loading...