RM0367 Rev 7 107/1043

RM0367 Flash program memory and data EEPROM (FLASH)

122

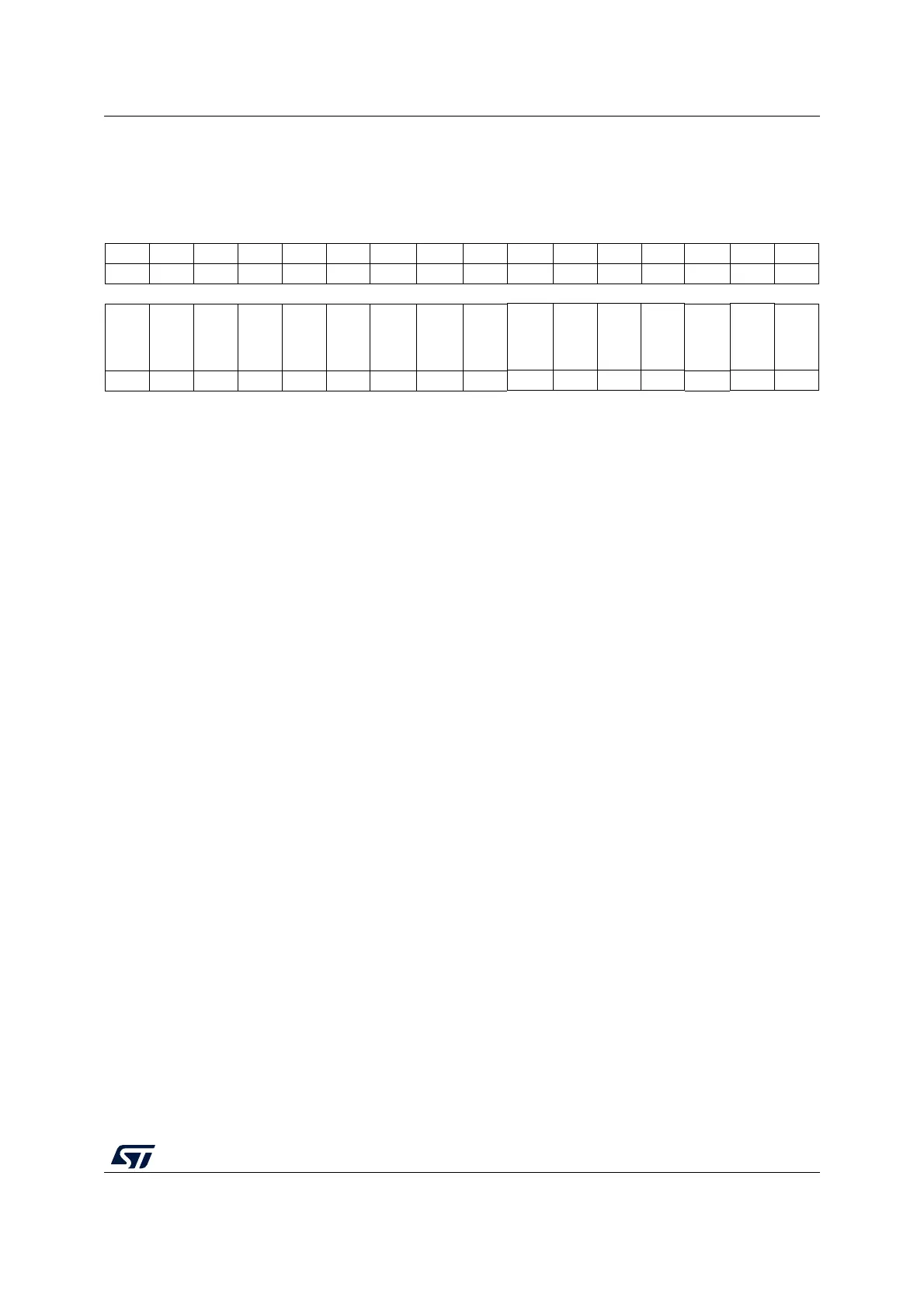

3.7.1 Access control register (FLASH_ACR)

Address offset: 0x00

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

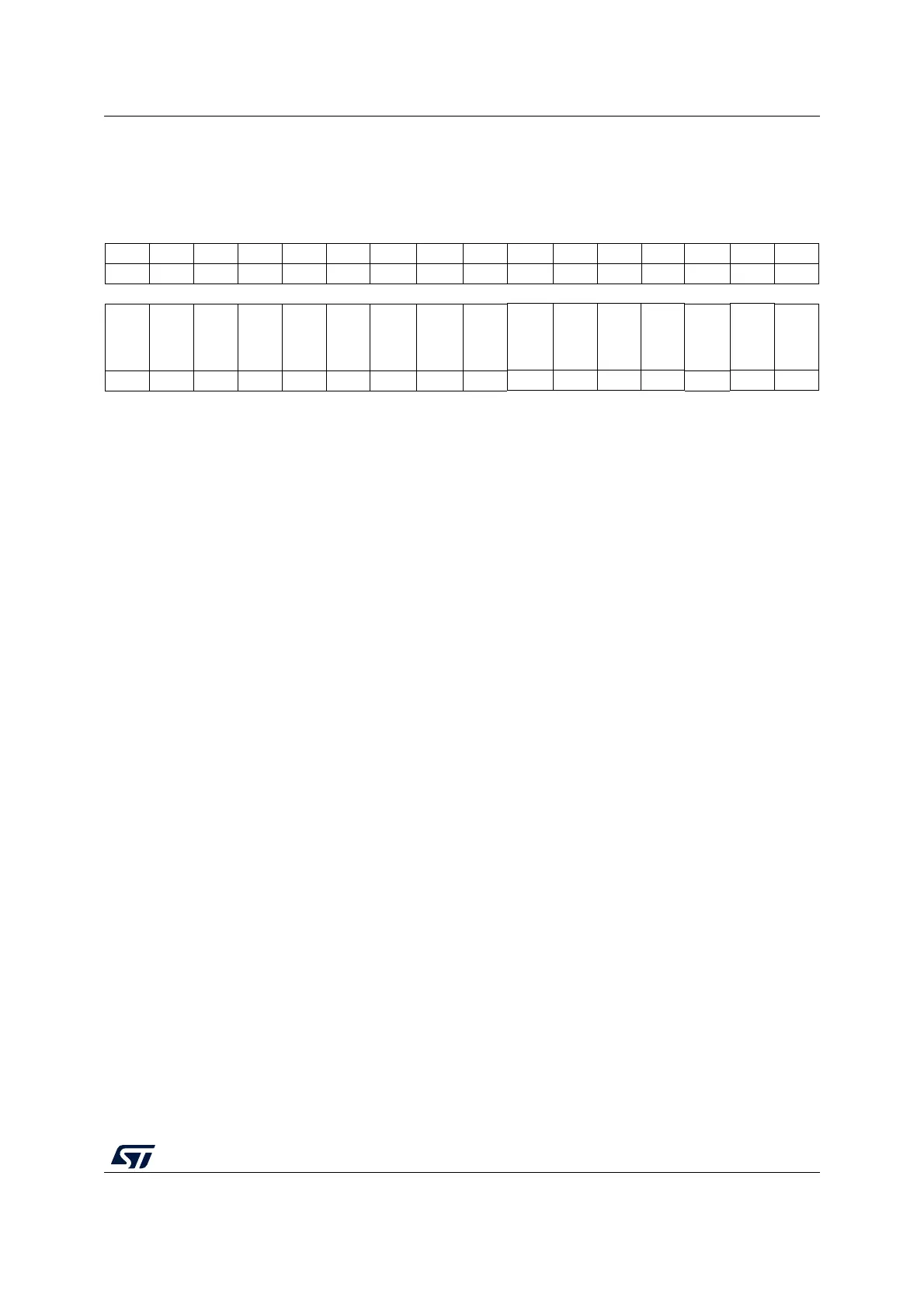

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res.

PRE_READ

DISAB_BUF

RUN_PD

SLEEP_PD

Res.

PRFTEN

LATENCY

rw rw rw rw rw rw

Bits 31:7 Reserved, must be kept at reset value

Bit 6 PRE_READ

This bit enables the pre-read.

0: The pre-read is disabled

1: The pre-read is enabled. The memory interface stores the last address read as data and

tries to read the next one when no other read or write or prefetch operation is ongoing.

Note: It is automatically reset every time the DISAB_BUF bit (in this register) is set to 1.

Bit 5 DISAB_BUF

This bit disables the buffers used as a cache during a read. This means that every read will

access the NVM even for an address already read (for example, the previous address). When

this bit is reset, the PRFTEN and PRE_READ bits are automatically reset, too.

0: The buffers are enabled

1: The buffers are disabled. Every time one NVM value is necessary, one new memory read

sequence has do be done.

Bit 4 RUN_PD

This bit determines if the NVM is in power-down mode or in idle mode when the device is in run

mode. It is possible to write this bit only when there is an unlocked writing of the

FLASH_PDKEYR register.

The correct sequence is explained in Section 3.6.4: Power-down. When writing this bit to 0, the

keys are automatically lost and a new unlock sequence is necessary to re-write it to 1.

0: When the device is in Run mode, the NVM is in Idle mode.

1: When the device is in Run mode, the NVM is in power-down mode.

Bit 3 SLEEP_PD

This bit allows to have the Flash program memory and data EEPROM in power-down mode or

in idle mode when the device is in Sleep mode.

0: When the device is in Sleep mode, the NVM is in Idle mode.

1: When the device is in Sleep mode, the NVM is in power-down mode.

Loading...

Loading...