Digital-to-analog converter (DAC) RM0367

364/1043 RM0367 Rev 7

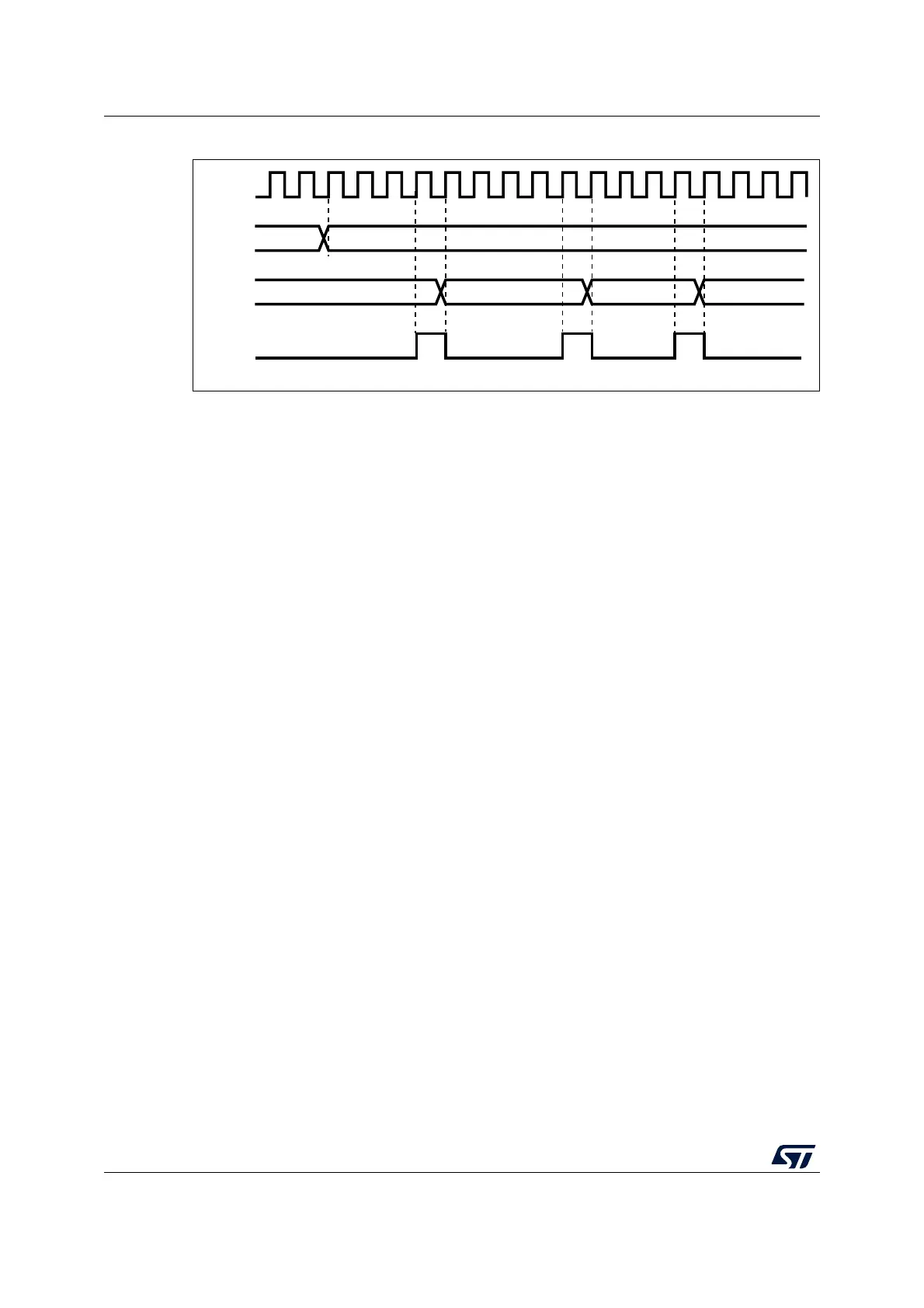

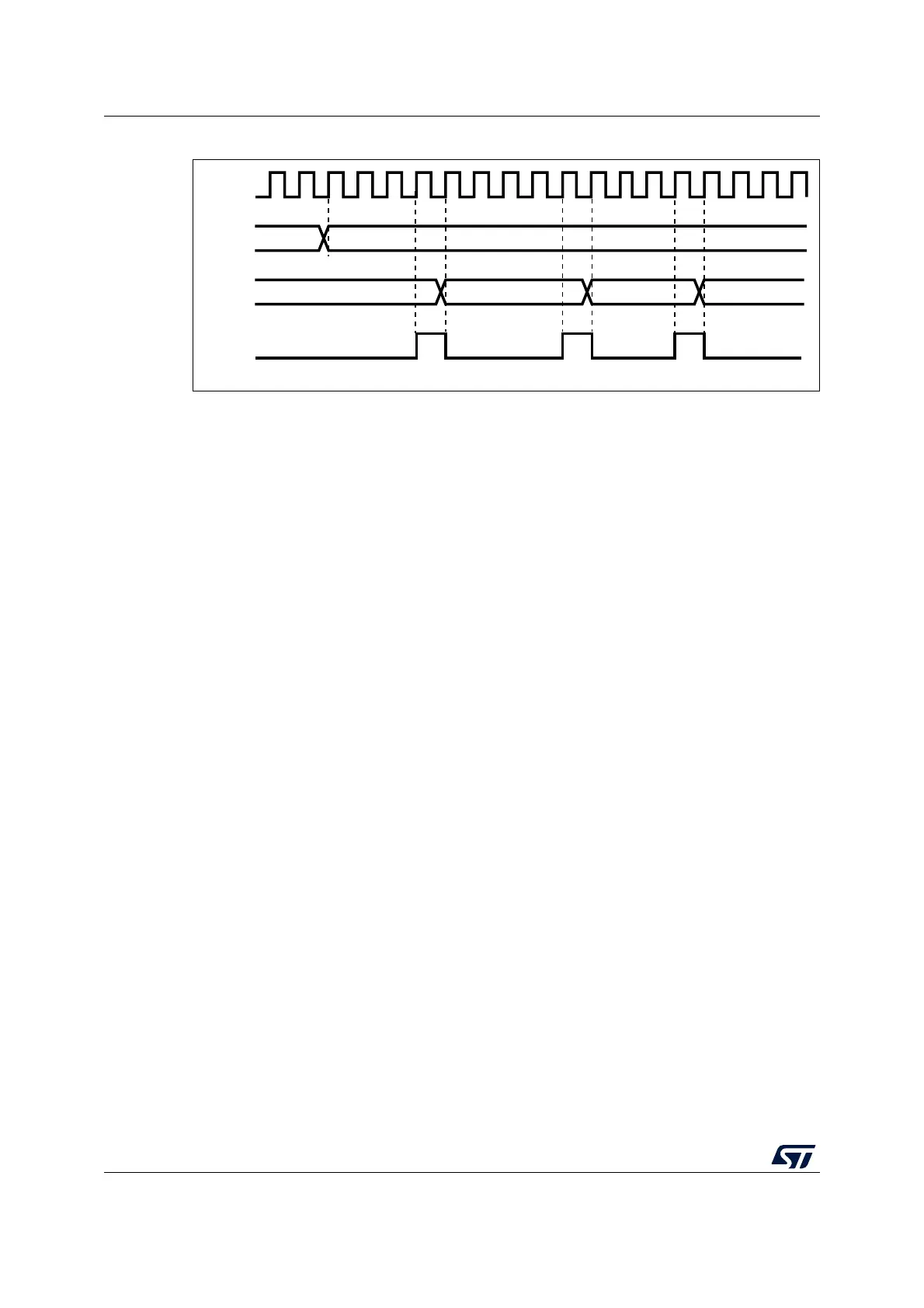

Figure 65. DAC conversion (SW trigger enabled) with triangle wave generation

Note: The DAC trigger must be enabled for triangle generation by setting the TENx bit in the

DAC_CR register.

The MAMPx[3:0] bits must be configured before enabling the DAC, otherwise they cannot

be changed.

15.9 DMA request

Each DAC channel has a DMA capability. Two DMA channels are used to service DAC

channel DMA requests.

A DAC DMA request is generated when an external trigger (but not a software trigger)

occurs while the DMAENx bit is set. The value of the DAC_DHRx register is then transferred

to the DAC_DORx register.

In dual mode, if both DMAENx bits are set, two DMA requests are generated. If only one

DMA request is needed, user should set only the corresponding DMAENx bit. In this way,

the application can manage both DAC channels in dual mode by using one DMA request

and a unique DMA channel.

DMA underrun

The DAC DMA request is not queued so that if a second external trigger arrives before the

acknowledgment for the first external trigger is received (first request), then no new request

is issued and the DMA channelx underrun flag DMAUDRx in the DAC_SR register is set,

reporting the error condition. DMA data transfers are then disabled and no further DMA

request is treated. The DAC channelx continues to convert old data.

The software should clear the DMAUDRx flag by writing “1”, clear the DMAEN bit of the

used DMA stream and re-initialize both DMA and DAC channelx to restart the transfer

correctly. The software should modify the DAC trigger conversion frequency or lighten the

DMA workload to avoid a new DMA. Finally, the DAC conversion can be resumed by

enabling both DMA data transfer and conversion trigger.

For each DAC channel, an interrupt is also generated if the corresponding DMAUDRIEx bit

in the DAC_CR register is enabled.

For code example, refer to A.9.3: DMA initialization code example.

APB1_CLK

0xABE

0xABE

DHR

DOR

ai14716b

0xABF

SWTRIG

0xAC0

Loading...

Loading...