Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0367

782/1043 RM0367 Rev 7

where

DWU is the error due to sampling point deviation when the wakeup from Stop mode is

used.

when M[1:0] = 01:

when M[1:0] = 00:

when M[1:0] = 10:

t

WUUSART

is the time between:

– The detection of start bit falling edge

– The instant when clock (requested by the peripheral) is ready and reaching the

peripheral and regulator is ready.

t

WUUSART

corresponds to t

WUSTOP

value provided in the datasheet.

The USART receiver can receive data correctly at up to the maximum tolerated

deviation specified in Table 142 and Table 143 depending on the following choices:

• 9-, 10- or 11-bit character length defined by the M bits in the USART_CR1 register

• Oversampling by 8 or 16 defined by the OVER8 bit in the USART_CR1 register

• Bits BRR[3:0] of USART_BRR register are equal to or different from 0000.

• Use of 1 bit or 3 bits to sample the data, depending on the value of the ONEBIT bit in

the USART_CR3 register.

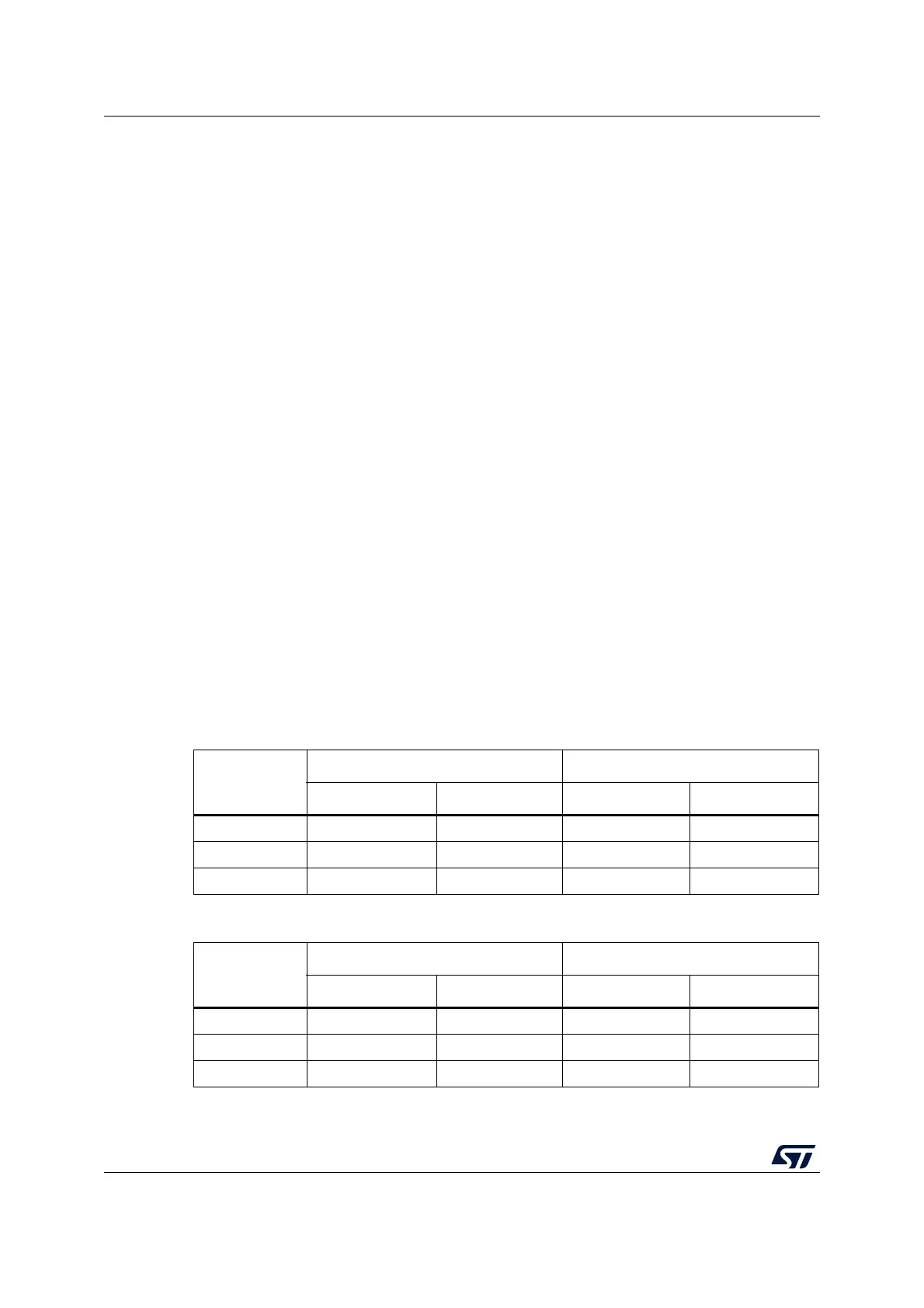

Table 142. Tolerance of the USART receiver when BRR [3:0] = 0000

M bits

OVER8 bit = 0 OVER8 bit = 1

ONEBIT=0 ONEBIT=1 ONEBIT=0 ONEBIT=1

00 3.75% 4.375% 2.50% 3.75%

01 3.41% 3.97% 2.27% 3.41%

10 4.16% 4.86% 2.77% 4.16%

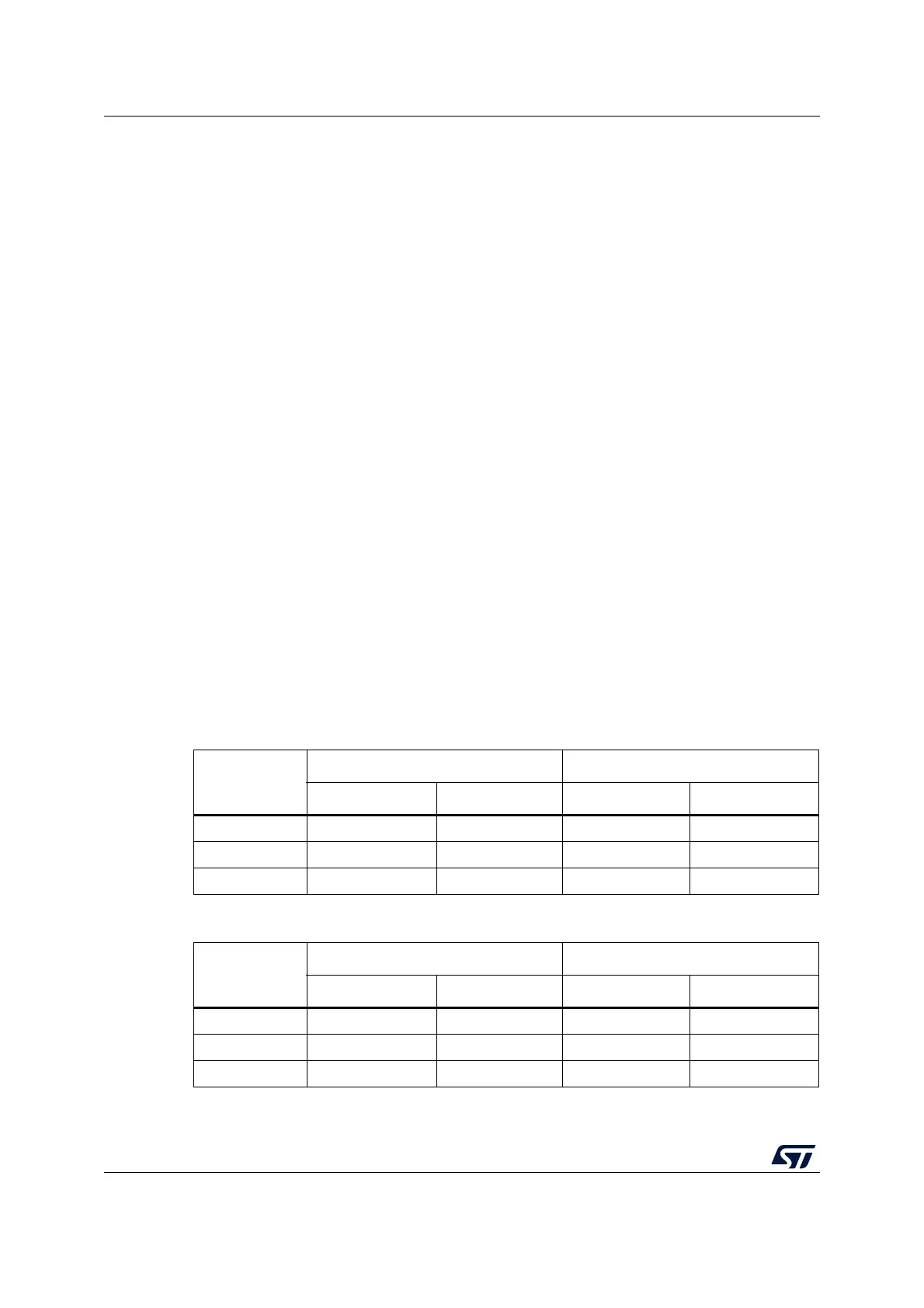

Table 143. Tolerance of the USART receiver when BRR [3:0] is different from 0000

M bits

OVER8 bit = 0 OVER8 bit = 1

ONEBIT=0 ONEBIT=1 ONEBIT=0 ONEBIT=1

00 3.33% 3.88% 2% 3%

01 3.03% 3.53% 1.82% 2.73%

10 3.7% 4.31% 2.22% 3.33%

DWU

t

WUUSART

11 Tbit×

---------------------------=

DWU

t

WUUSART

10 Tbit×

---------------------------=

DWU

t

WUUSART

9Tbit×

---------------------------=

Loading...

Loading...