Direct memory access controller (DMA) RM0367

268/1043 RM0367 Rev 7

11.4 DMA functional description

11.4.1 DMA block diagram

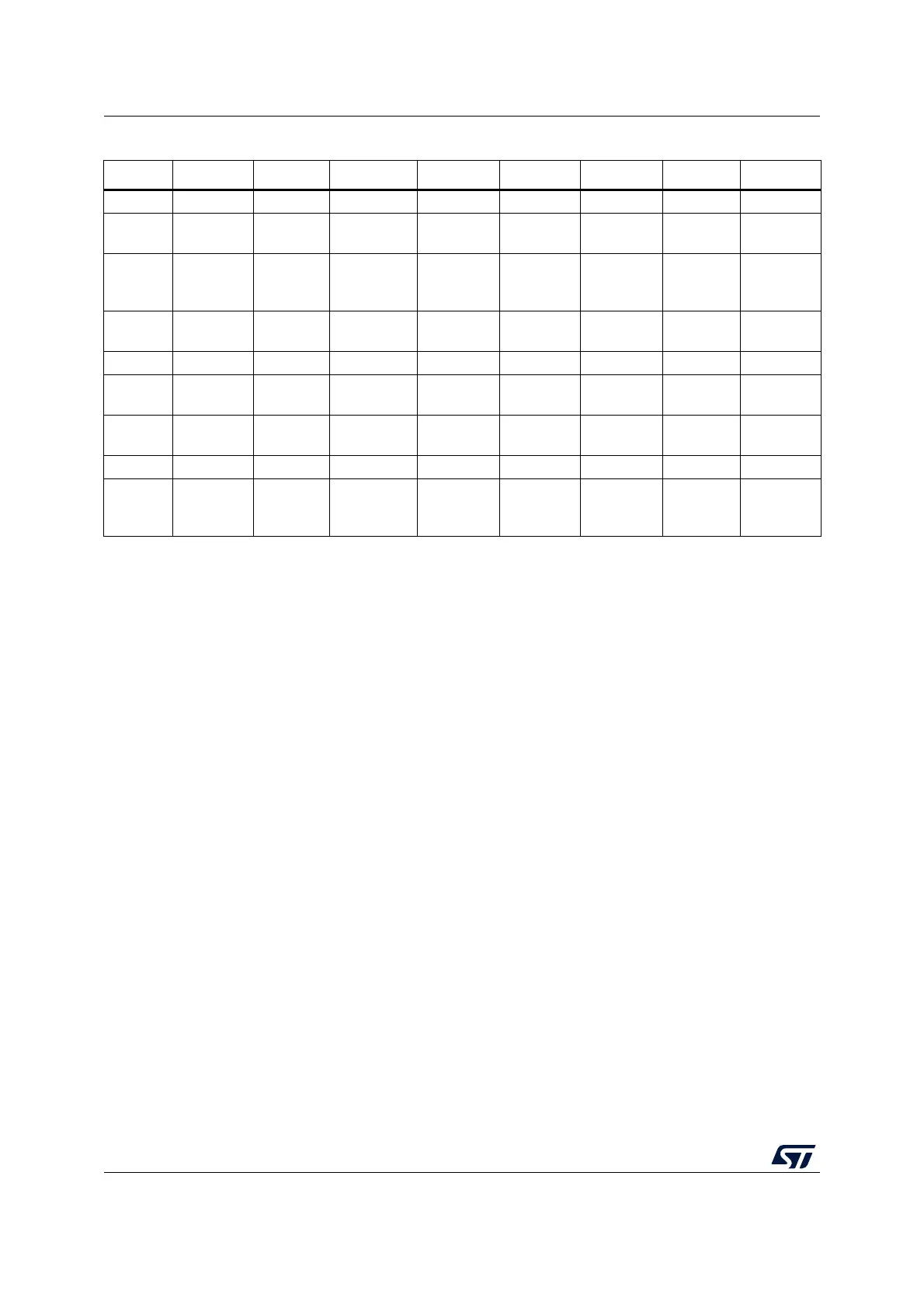

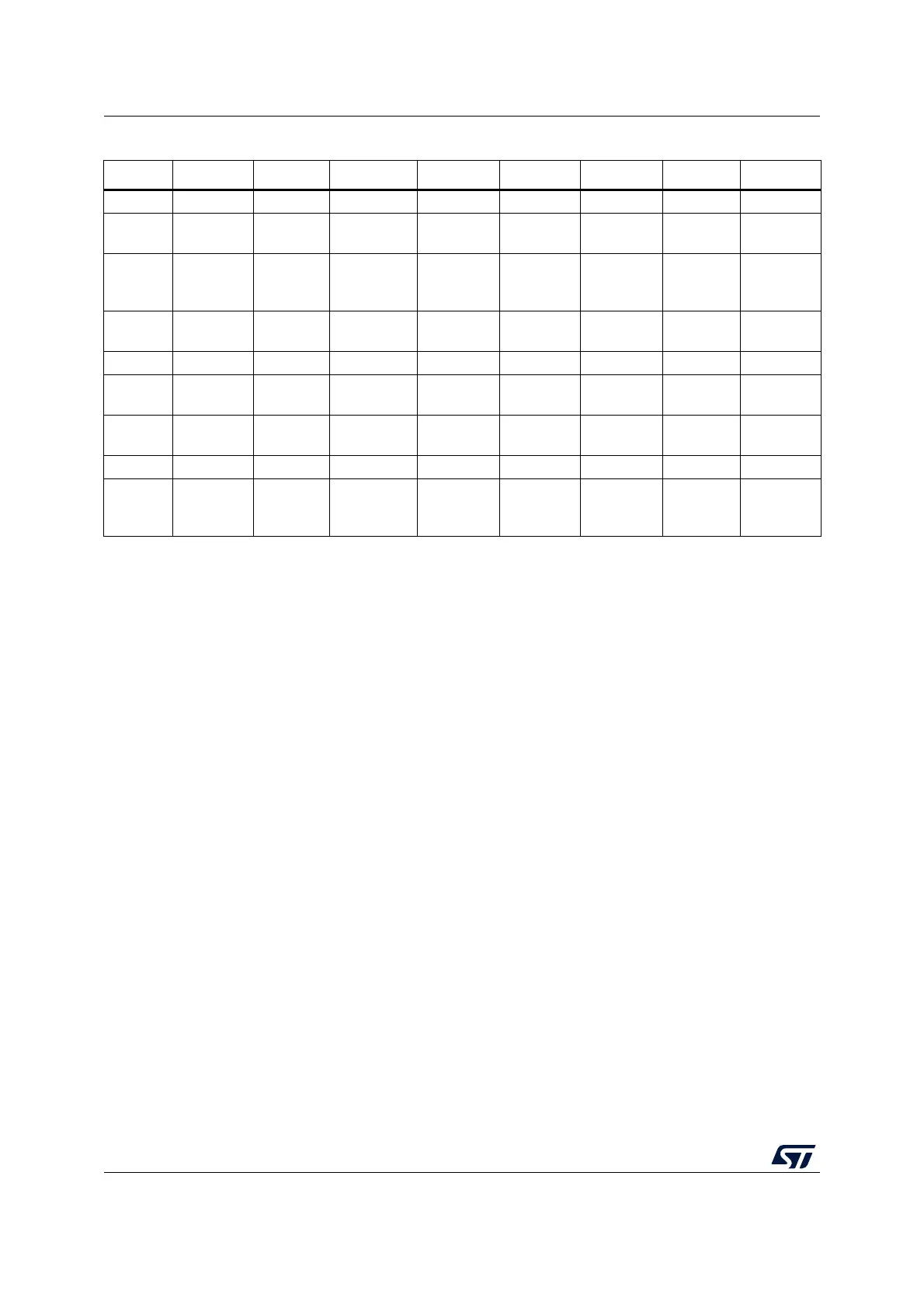

0111 I2C2 - - - I2C2_TX I2C2_RX - -

1000 TIM2

TIM2_

CH3

TIM2_UP TIM2_CH2 TIM2_CH4 TIM2_CH1 -

TIM2_CH2

TIM2_CH4

1001

TIM6_UP/

DAC_

channel1

-

TIM6_UP/

DAC_

channel1

-----

1010 TIM3 - TIM3_CH3

TIM3_CH4

TIM3_UP

- TIM3_CH1

TIM3_

TRIG

-

1011 AES

(1)

AES_IN AES_OUT AES_OUT - AES_IN - -

1100 USART4 -

USART4_

RX

USART4_

TX

--

USART4_

RX

USART4_

TX

1101 USART5 -

USART5_

RX

USART5_

TX

--

USART5_

RX

USART5_

TX

1110 I2C3 - I2C3_TX I2C3_RX I2C3_TX I2C3_RX - -

1111

TIM7_UP/

DAC_

channel2

-- -

TIM7_UP/

DAC_

channel2

---

1. Available only on category 3 and 5 with AES.

Table 51. DMA requests for each channel (continued)

CxS[3:0] Peripheral Channel 1 Channel 2 Channel 3 Channel 4 Channel 5 Channel 6 Channel 7

Loading...

Loading...