Digital-to-analog converter (DAC) RM0367

374/1043 RM0367 Rev 7

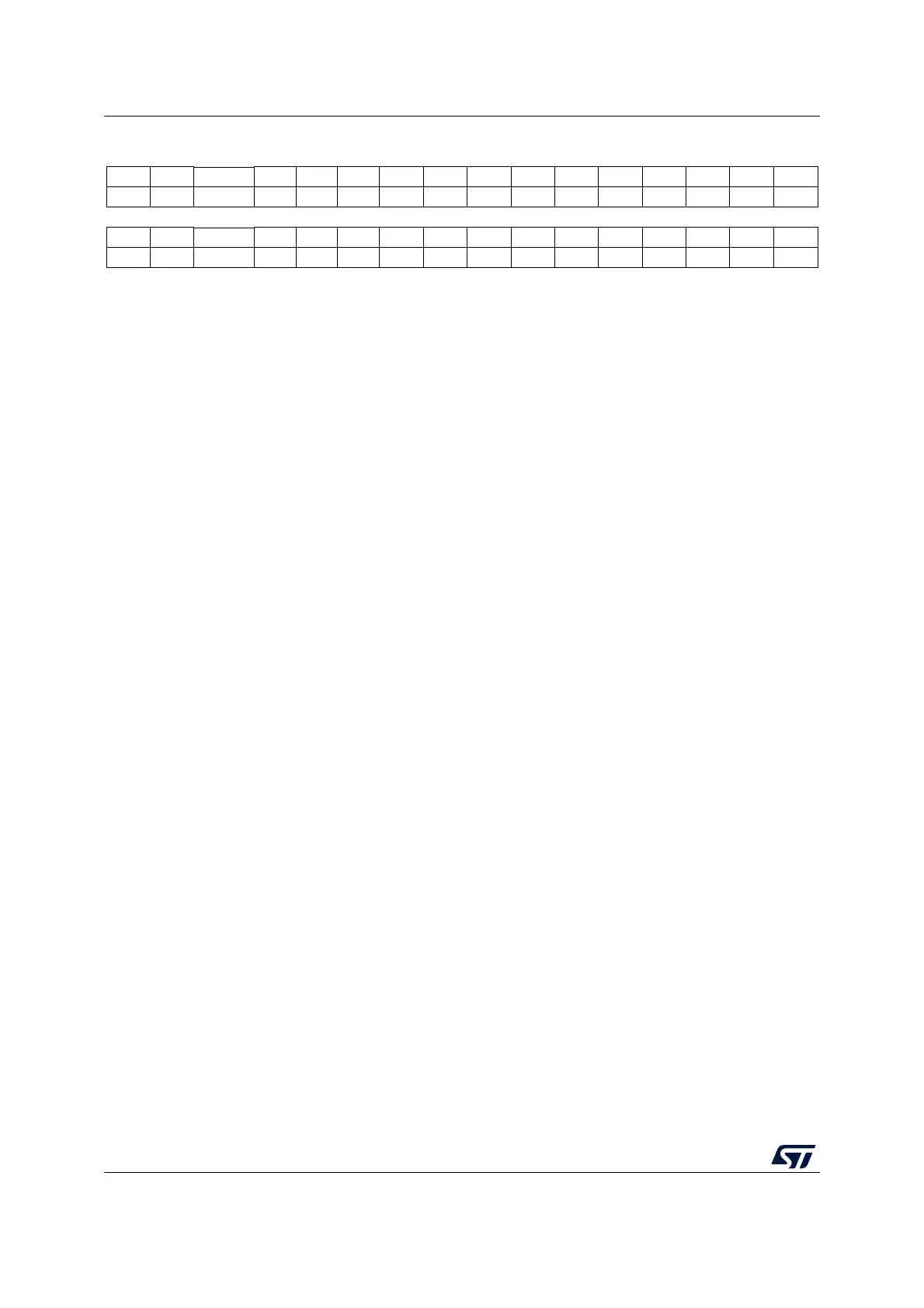

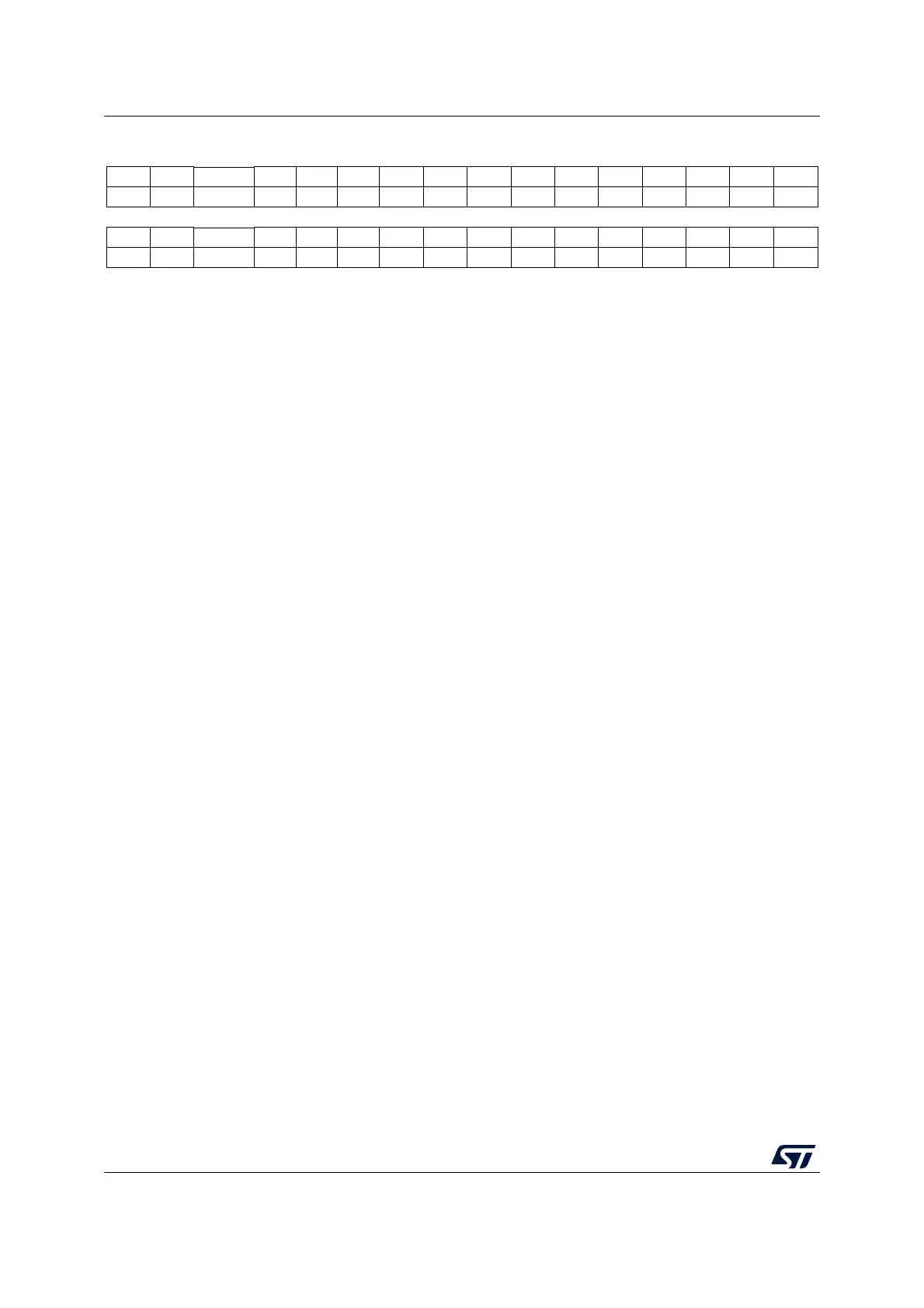

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. DMAUDR2 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rc_w1

1514 13 1211109876543210

Res. Res. DMAUDR1 Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rc_w1

Bits 31:30 Reserved, must be kept at reset value.

Bit 29 DMAUDR2: DAC channel2 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel2

1: DMA underrun error condition occurred for DAC channel2 (the currently selected trigger is

driving DAC channel2 conversion at a frequency higher than the DMA service capability rate)

Note: This bit is available in dual mode only. It is reserved in single mode.

Bits 28:14 Reserved, must be kept at reset value.

Bit 13 DMAUDR1: DAC channel1 DMA underrun flag

This bit is set by hardware and cleared by software (by writing it to 1).

0: No DMA underrun error condition occurred for DAC channel1

1: DMA underrun error condition occurred for DAC channel1 (the currently selected trigger is

driving DAC channel1 conversion at a frequency higher than the DMA service capability rate)

Bits 12:0 Reserved, must be kept at reset value.

Loading...

Loading...