Comparator (COMP) RM0367

380/1043 RM0367 Rev 7

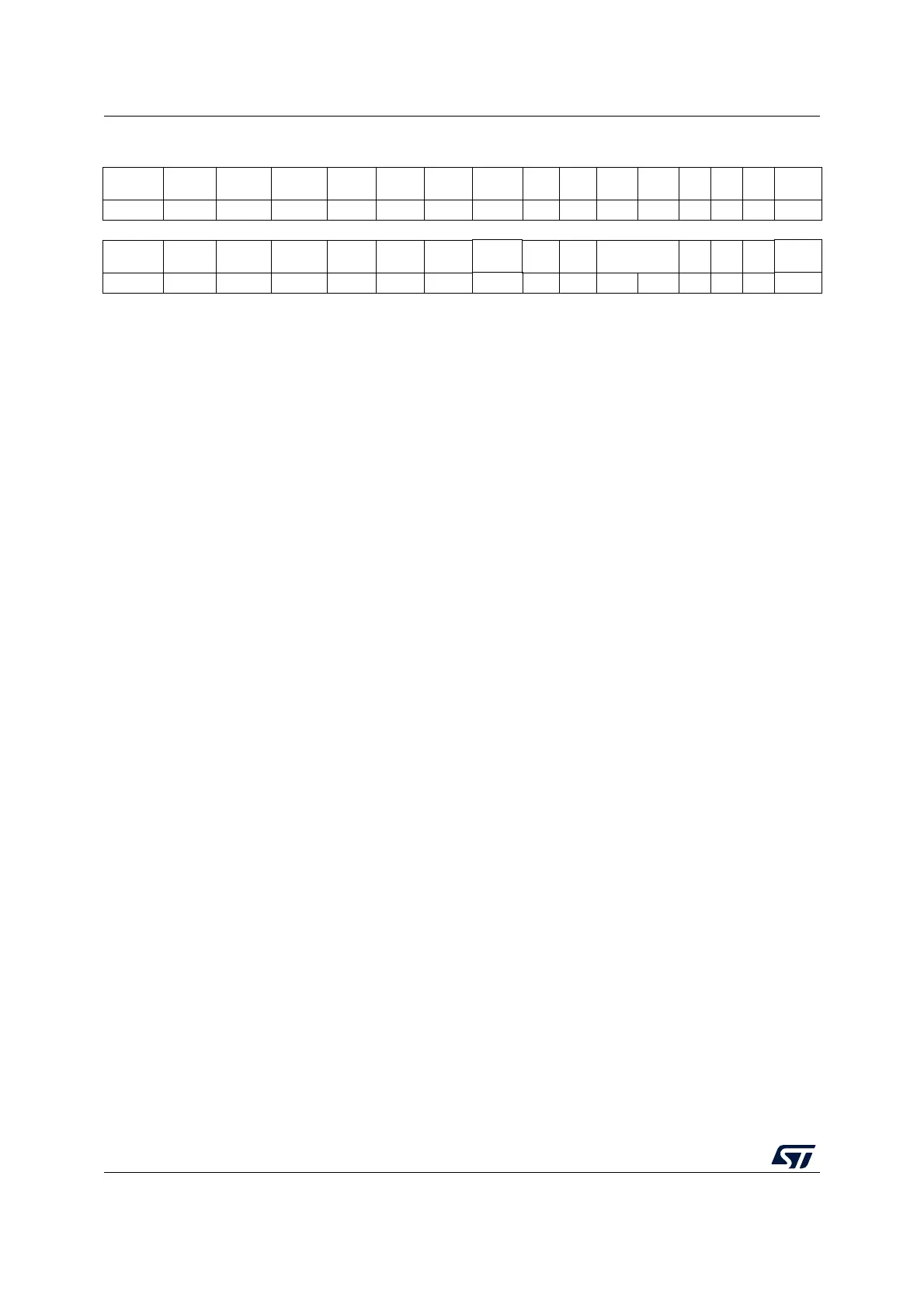

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

COMP1

LOCK

COMP1

VALUE

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rs r

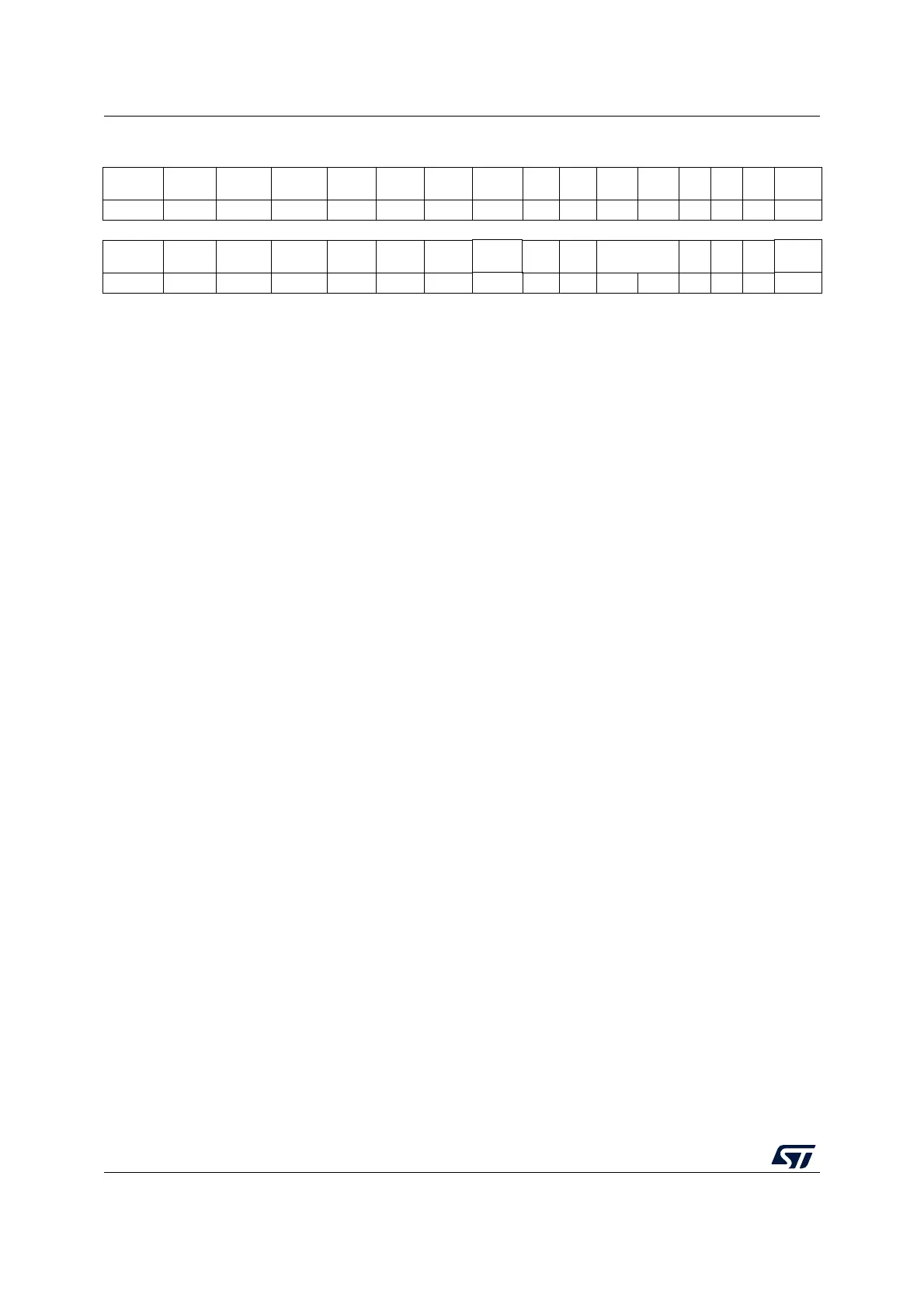

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

COMP1

POLARITY

Res. Res.

COMP1

LPTIMIN1

Res. Res. Res.

COMP1

WM

Res. Res.

COMP1INN

SEL

Res. Res. Res.

COMP1

EN

rw rw rw rw rw rw

Bit 31 COMP1LOCK: COMP1_CSR register lock bit

This bit is set by software and cleared by a hardware system reset. It locks the whole

content of the comparator 1 control register, COMP1_CSR[31:0]

0: COMP1_CSR[31:0] for comparator 1 are read/write

1: COMP1_CSR[31:0] for comparator 1 are read-only

Bit 30 COMP1VALUE: Comparator 1 output status bit

This bit is read-only. It reflects the current comparator 1 output taking into account

COMP1POLARITY bit effect.

Bits 29:16 Reserved, must be kept at reset value

Bit 15 COMP1POLARITY: Comparator 1 polarity selection bit

This bit is set and cleared by software (only if COMP1LOCK not set). It inverts Comparator

1 polarity.

0: Comparator 1 output value not inverted

1: Comparator 1output value inverted

Bits 14:13 Reserved, must be kept at reset value

Bit 12 COMP1LPTIMIN1: Comparator 1 LPTIM input propagation bit

This bit is set and cleared by software (assuming COMP1LOCK not set). It sends

COMP1VALUE to LPTIM input 1.

0: Comparator 1 output gated

1: Comparator 1 output sent to LPTIM input 1

Bits 11:9 Reserved, must be kept at reset value

Bit 8 COMP1WM: Comparator 1 window mode selection bit

This bit is set and cleared by software (only if COMP1LOCK not set). It selects comparator

1 window mode where the Plus inputs of both comparators are connected together.

0: Plus input of comparator 1 connected to PA1.

1: Plus input of comparator 1 shorted with Plus input of comparator 2 (see COMP1_CSR).

Bits 7:6 Reserved, must be kept at reset value

Loading...

Loading...