RM0367 Rev 7 827/1043

RM0367 Universal synchronous/asynchronous receiver transmitter (USART/UART)

872

29.8.9 USART interrupt flag clear register (USART_ICR)

Address offset: 0x20

Reset value: 0x0000 0000

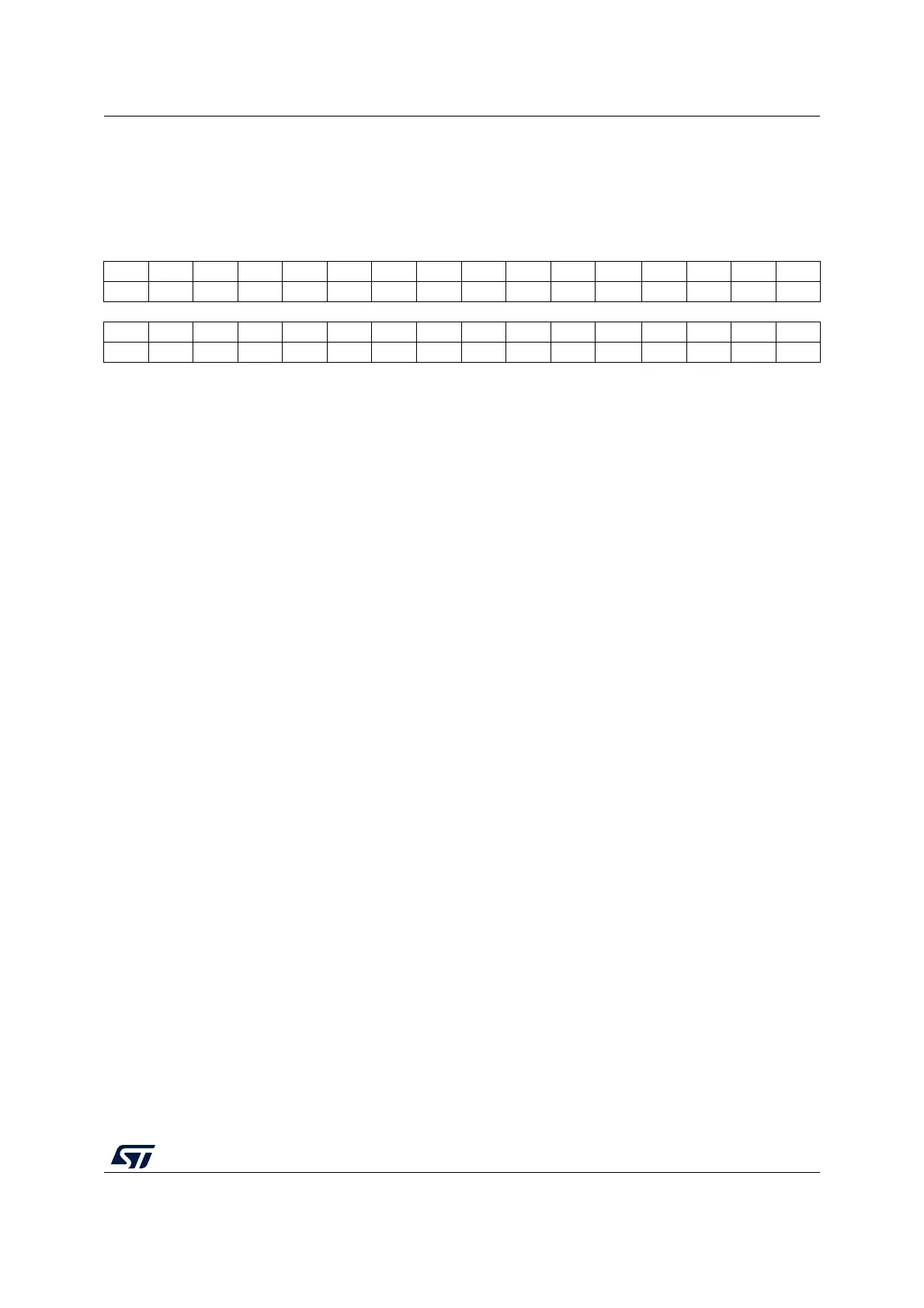

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. WUCF Res. Res. CMCF Res.

rc_w1 rc_w1

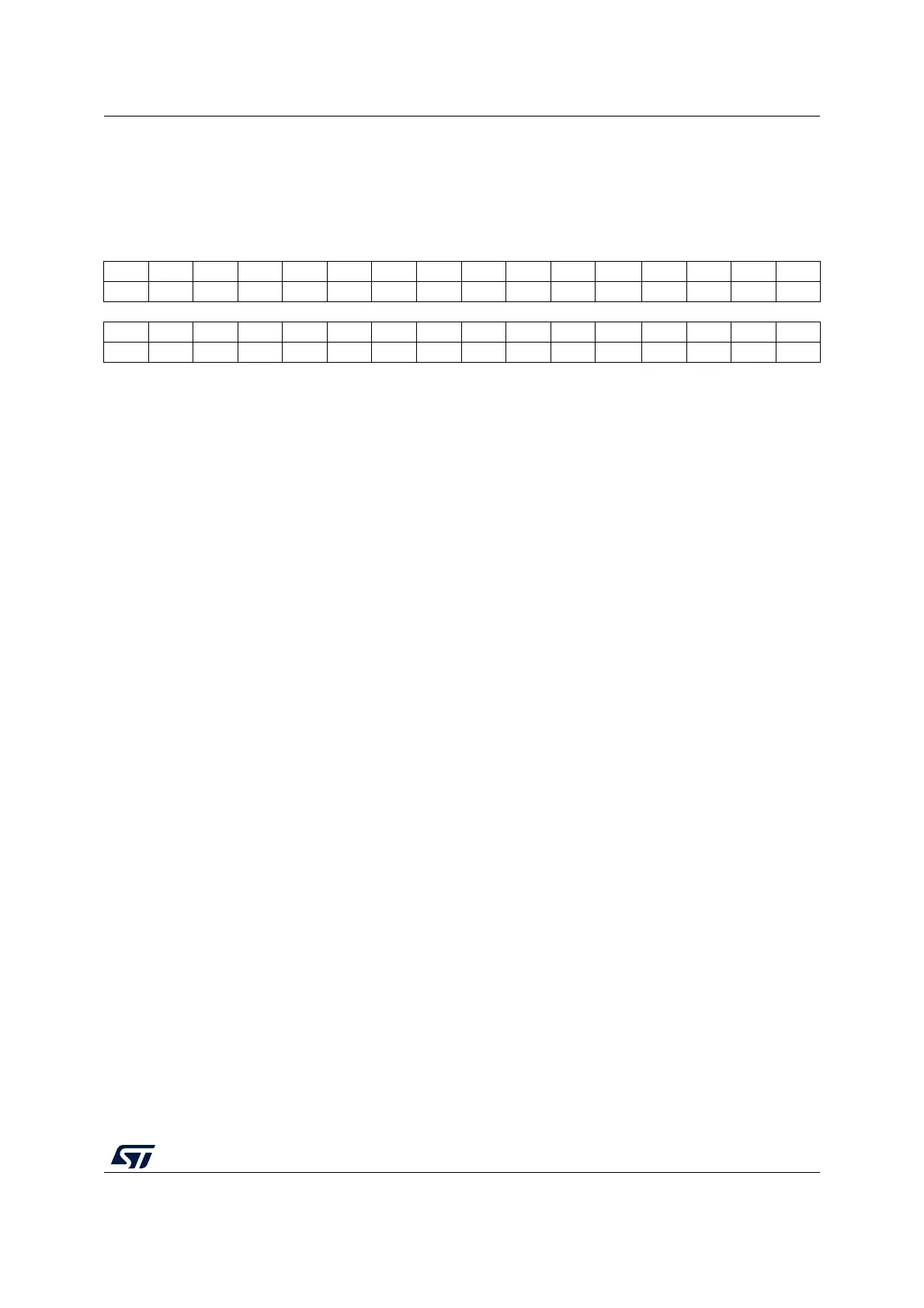

1514131211109876543210

Res. Res. Res. EOBCF RTOCF Res. CTSCF LBDCF Res. TCCF Res. IDLECF ORECF NCF FECF PECF

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Bits 31:21 Reserved, must be kept at reset value.

Bit 20 WUCF: Wakeup from Stop mode clear flag

Writing 1 to this bit clears the WUF flag in the USART_ISR register.

Note: If the USART does not support the wakeup from Stop feature, this bit is reserved and

must be kept at reset value.

Bits 19:18 Reserved, must be kept at reset value.

Bit 17 CMCF: Character match clear flag

Writing 1 to this bit clears the CMF flag in the USART_ISR register.

Bits 16:13 Reserved, must be kept at reset value.

Bit 12 EOBCF: End of block clear flag

Writing 1 to this bit clears the EOBF flag in the USART_ISR register.

Note: If the USART does not support Smartcard mode, this bit is reserved and must be kept

at reset value. Please refer to Section 29.4: USART implementation on page 766.

Bit 11 RTOCF: Receiver timeout clear flag

Writing 1 to this bit clears the RTOF flag in the USART_ISR register.

Note: If the USART does not support the Receiver timeout feature, this bit is reserved and

must be kept at reset value. Please refer to Section 29.4: USART implementation on

page 766.

Bit 10 Reserved, must be kept at reset value.

Bit 9 CTSCF: CTS clear flag

Writing 1 to this bit clears the CTSIF flag in the USART_ISR register.

Note: If the hardware flow control feature is not supported, this bit is reserved and must be

kept at reset value. Please refer to Section 29.4: USART implementation on page 766.

Bit 8 LBDCF: LIN break detection clear flag

Writing 1 to this bit clears the LBDF flag in the USART_ISR register.

Note: If LIN mode is not supported, this bit is reserved and must be kept at reset value.

Please refer to Section 29.4: USART implementation on page 766.

Bit 7 Reserved, must be kept at reset value.

Bit 6 TCCF: Transmission complete clear flag

Writing 1 to this bit clears the TC flag in the USART_ISR register.

Bit 5 Reserved, must be kept at reset value.

Bit 4 IDLECF: Idle line detected clear flag

Writing 1 to this bit clears the IDLE flag in the USART_ISR register.

Loading...

Loading...