Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0367

828/1043 RM0367 Rev 7

29.8.10 USART receive data register (USART_RDR)

Address offset: 0x24

Reset value: 0x0000 0000

29.8.11 USART transmit data register (USART_TDR)

Address offset: 0x28

Reset value: 0x0000 0000

Bit 3 ORECF: Overrun error clear flag

Writing 1 to this bit clears the ORE flag in the USART_ISR register.

Bit 2 NCF: Noise detected clear flag

Writing 1 to this bit clears the NF flag in the USART_ISR register.

Bit 1 FECF: Framing error clear flag

Writing 1 to this bit clears the FE flag in the USART_ISR register.

Bit 0 PECF: Parity error clear flag

Writing 1 to this bit clears the PE flag in the USART_ISR register.

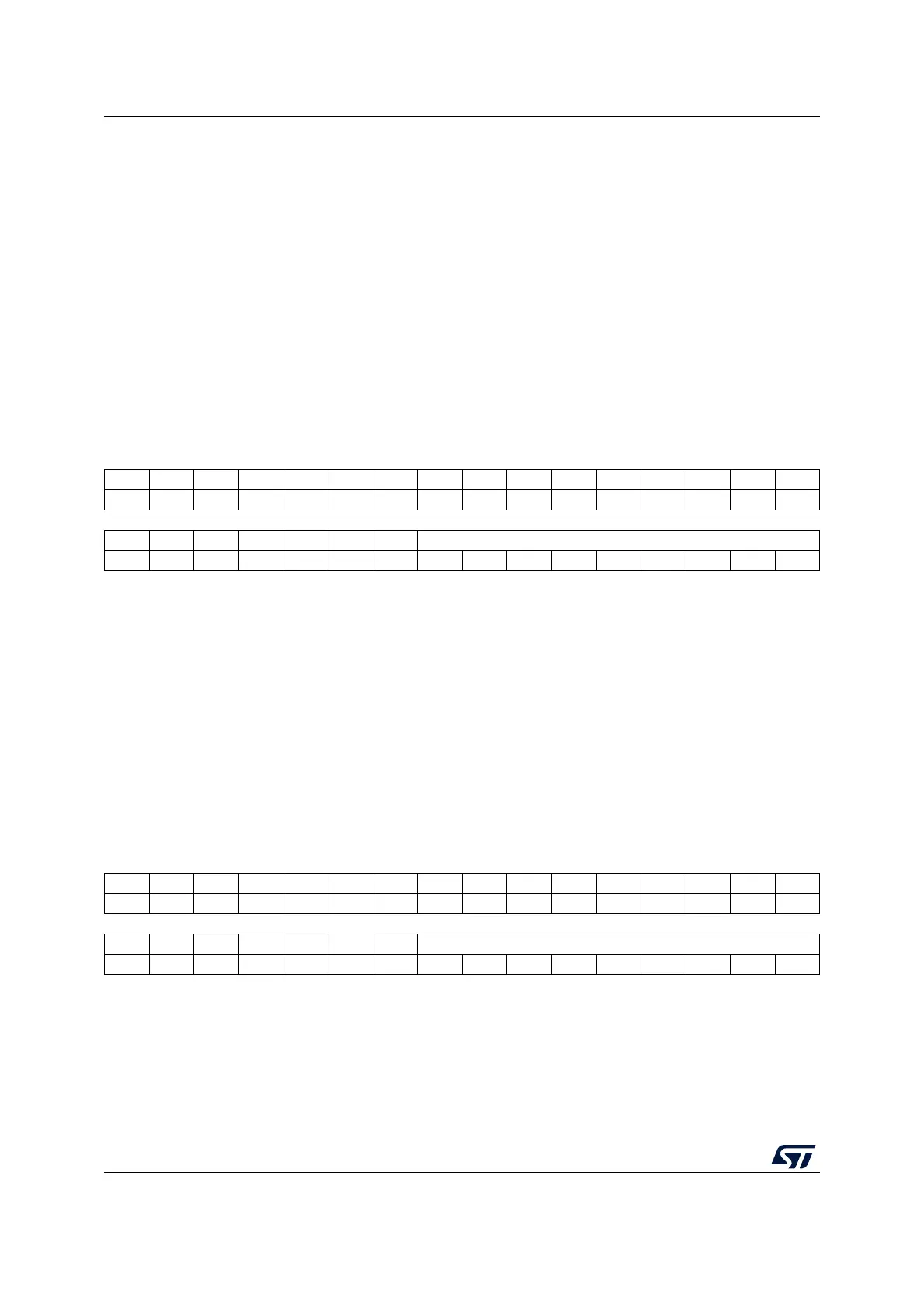

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. RDR[8:0]

rrrrrrrrr

Bits 31:9 Reserved, must be kept at reset value.

Bits 8:0 RDR[8:0]: Receive data value

Contains the received data character.

The RDR register provides the parallel interface between the input shift register and the

internal bus (see Figure 242).

When receiving with the parity enabled, the value read in the MSB bit is the received parity

bit.

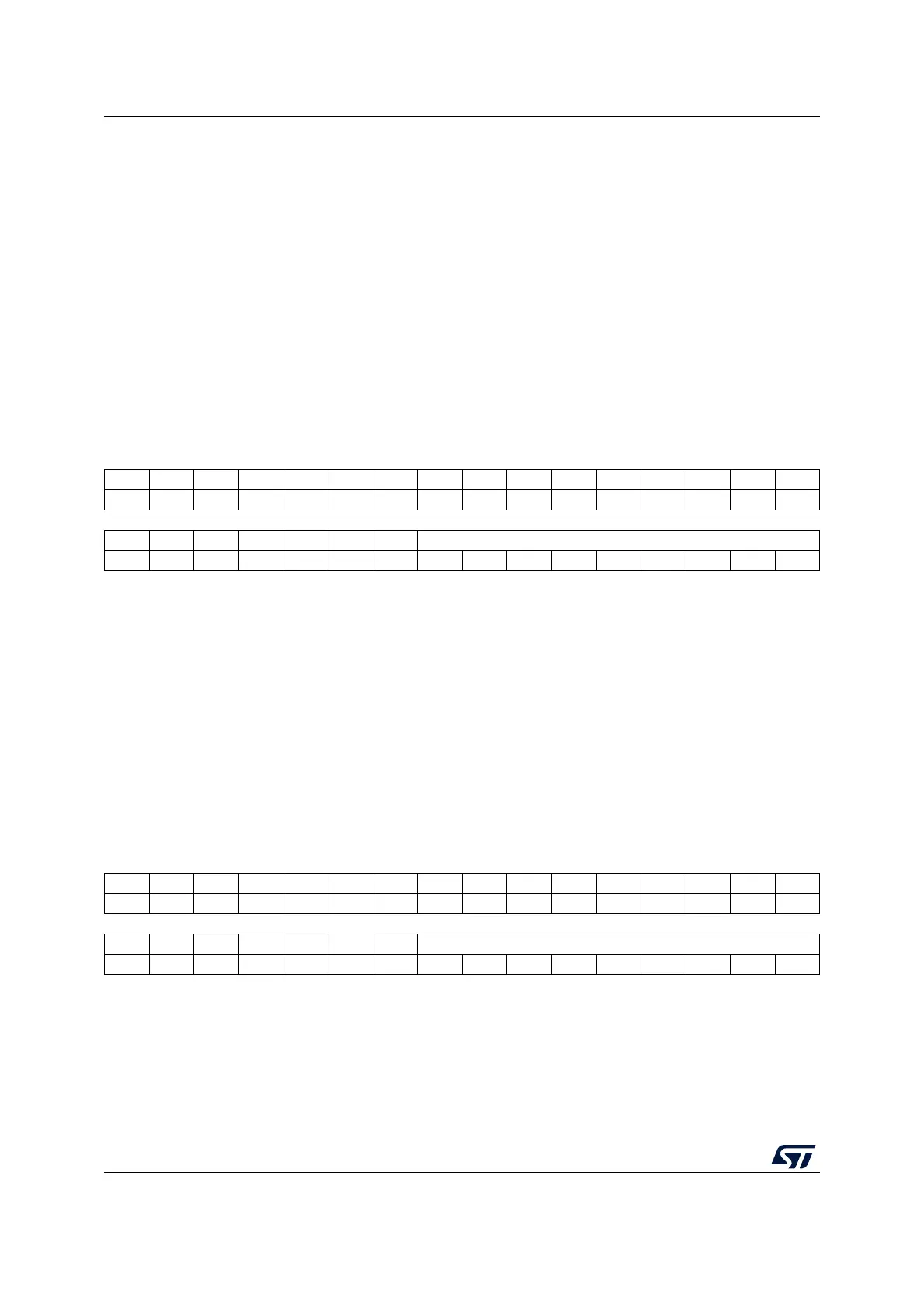

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. TDR[8:0]

rw rw rw rw rw rw rw rw rw

Loading...

Loading...