RM0367 Rev 7 863/1043

RM0367 Low-power universal asynchronous receiver transmitter (LPUART)

872

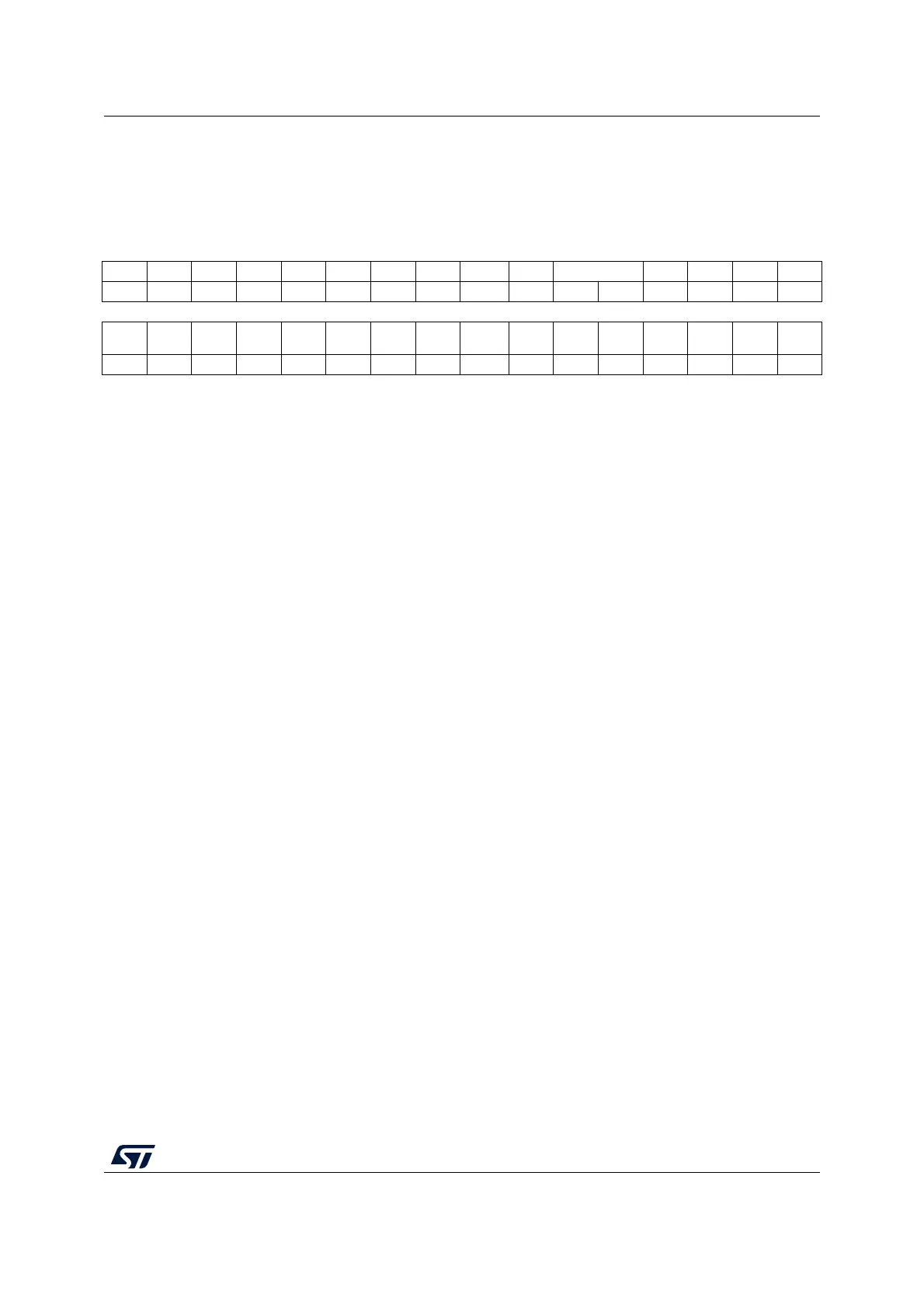

30.7.3 Control register 3 (LPUART_CR3)

Address offset: 0x08

Reset value: 0x0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. UCESM WUFIE WUS[2:0] Res. Res. Res. Res.

rw rw rw rw

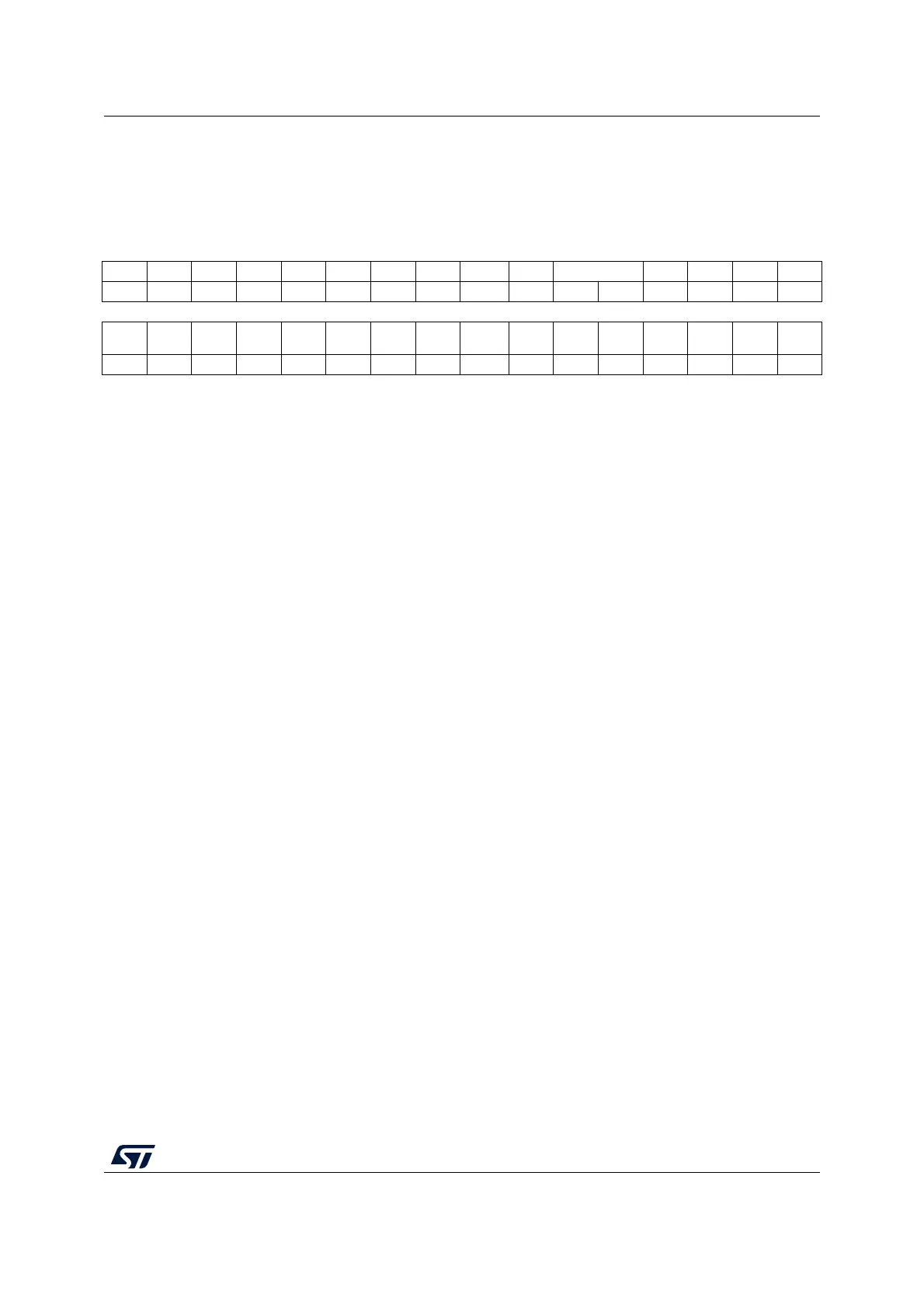

15141312111098 7 6543210

DEP DEM DDRE

OVR

DIS

Res. CTSIE CTSE RTSE DMAT DMAR Res. Res.

HD

SEL

Res. Res. EIE

rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 UCESM: LPUART Clock Enable in Stop mode.

This bit is set and cleared by software.

0: LPUART Clock is disabled in STOP mode.

1: LPUART Clock is enabled in STOP mode.

Note: In order to be able to wakeup the MCU from Stop mode with LPUART at 9600 baud,

the UCESM bit must be set prior to entering the Stop mode.

Bit 22 WUFIE: Wakeup from Stop mode interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An LPUART interrupt is generated whenever WUF=1 in the LPUART_ISR register

Note: WUFIE must be set before entering in Stop mode.

The WUF interrupt is active only in Stop mode.

If the LPUART does not support the wakeup from Stop feature, this bit is reserved and

must be kept at reset value.

Bits 21:20 WUS[1:0]: Wakeup from Stop mode interrupt flag selection

This bit-field specify the event which activates the WUF (wakeup from Stop mode flag).

00: WUF active on address match (as defined by ADD[7:0] and ADDM7)

01:Reserved.

10: WUF active on Start bit detection

11: WUF active on RXNE.

This bit field can only be written when the LPUART is disabled (UE=0).

Note: If the LPUART does not support the wakeup from Stop feature, this bit is reserved and

must be kept at reset value.

Bits 19:16 Reserved, must be kept at reset value.

Bit 15 DEP: Driver enable polarity selection

0: DE signal is active high.

1: DE signal is active low.

This bit can only be written when the LPUART is disabled (UE=0).

Bit 14 DEM: Driver enable mode

This bit allows the user to activate the external transceiver control, through the DE signal.

0: DE function is disabled.

1: DE function is enabled. The DE signal is output on the RTS pin.

This bit can only be written when the LPUART is disabled (UE=0).

Loading...

Loading...