Low-power universal asynchronous receiver transmitter (LPUART) RM0367

866/1043 RM0367 Rev 7

30.7.6 Interrupt & status register (LPUART_ISR)

Address offset: 0x1C

Reset value: 0x00C0

Bits 31:4 Reserved, must be kept at reset value

Bit 3 RXFRQ: Receive data flush request

Writing 1 to this bit clears the RXNE flag.

This allows to discard the received data without reading it, and avoid an overrun condition.

Bit 2 MMRQ: Mute mode request

Writing 1 to this bit puts the LPUART in mute mode and resets the RWU flag.

Bit 1 SBKRQ: Send break request

Writing 1 to this bit sets the SBKF flag and request to send a BREAK on the line, as soon as

the transmit machine is available.

Note: In the case the application needs to send the break character following all previously

inserted data, including the ones not yet transmitted, the software should wait for the

TXE flag assertion before setting the SBKRQ bit.

Bit 0 Reserved, must be kept at reset value

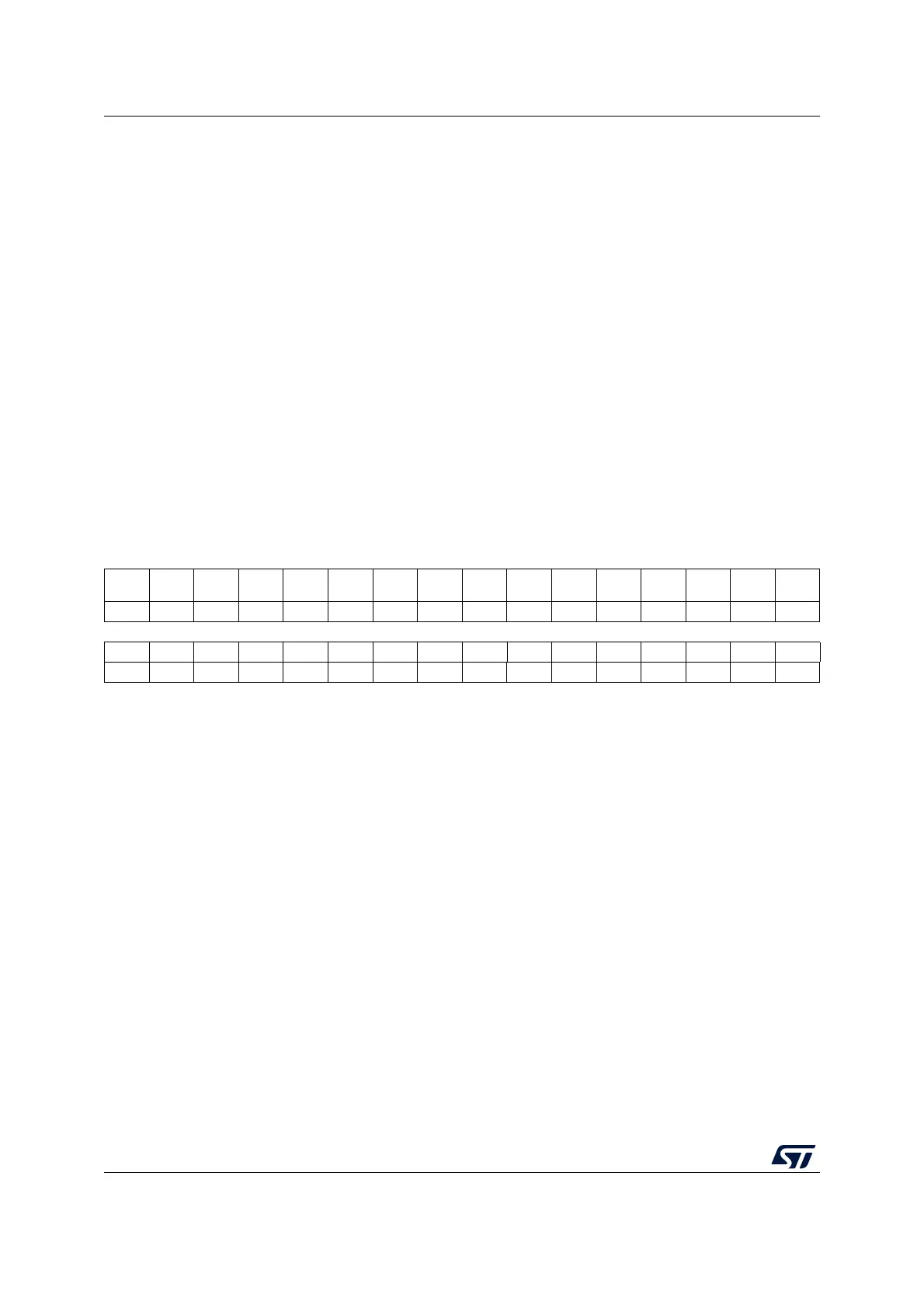

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res.

RE

ACK

TE

ACK

WUF RWU SBKF CMF BUSY

rrrrrrr

1514131211109876543210

Res. Res. Res. Res. Res. CTS CTSIF Res. TXE TC RXNE IDLE ORE NF FE PE

rr rrrrrrrr

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 REACK: Receive enable acknowledge flag

This bit is set/reset by hardware, when the Receive Enable value is taken into account by

the LPUART.

It can be used to verify that the LPUART is ready for reception before entering Stop mode.

Note: If the LPUART does not support the wakeup from Stop feature, this bit is reserved and

kept at reset value.

Bit 21 TEACK: Transmit enable acknowledge flag

This bit is set/reset by hardware, when the Transmit Enable value is taken into account by

the LPUART.

It can be used when an idle frame request is generated by writing TE=0, followed by TE=1

in the LPUART_CR1 register, in order to respect the TE=0 minimum period.

Bit 20 WUF: Wakeup from Stop mode flag

This bit is set by hardware, when a wakeup event is detected. The event is defined by the

WUS bit field. It is cleared by software, writing a 1 to the WUCF in the LPUART_ICR register.

An interrupt is generated if WUFIE=1 in the LPUART_CR3 register.

Note: When UESM is cleared, WUF flag is also cleared.

The WUF interrupt is active only in Stop mode.

If the LPUART does not support the wakeup from Stop feature, this bit is reserved and

kept at reset value.

Loading...

Loading...