RM0367 Rev 7 865/1043

RM0367 Low-power universal asynchronous receiver transmitter (LPUART)

872

30.7.4 Baud rate register (LPUART_BRR)

This register can only be written when the LPUART is disabled (UE=0).

Address offset: 0x0C

Reset value: 0x0000

Note: It is forbidden to write values less than 0x300 in the LPUART_BRR register.

Provided that LPUARTx_BRR must be > = 0x300 and LPUART_BRR is 20-bit, a care

should be taken when generating high baud rates using high fck values. fck must be in the

range [3 x baud rate,.4096 x baud rate].

30.7.5 Request register (LPUART_RQR)

Address offset: 0x18

Reset value: 0x0000

Bit 3 HDSEL: Half-duplex selection

Selection of Single-wire Half-duplex mode

0: Half duplex mode is not selected

1: Half duplex mode is selected

This bit can only be written when the LPUART is disabled (UE=0).

Bits 2:1 Reserved, must be kept at reset value.

Bit 0 EIE: Error interrupt enable

Error Interrupt Enable Bit is required to enable interrupt generation in case of a framing

error, overrun error or noise flag (FE=1 or ORE=1 or NF=1 in the LPUART_ISR register).

0: Interrupt is inhibited

1: An interrupt is generated when FE=1 or ORE=1 or NF=1 in the LPUART_ISR register.

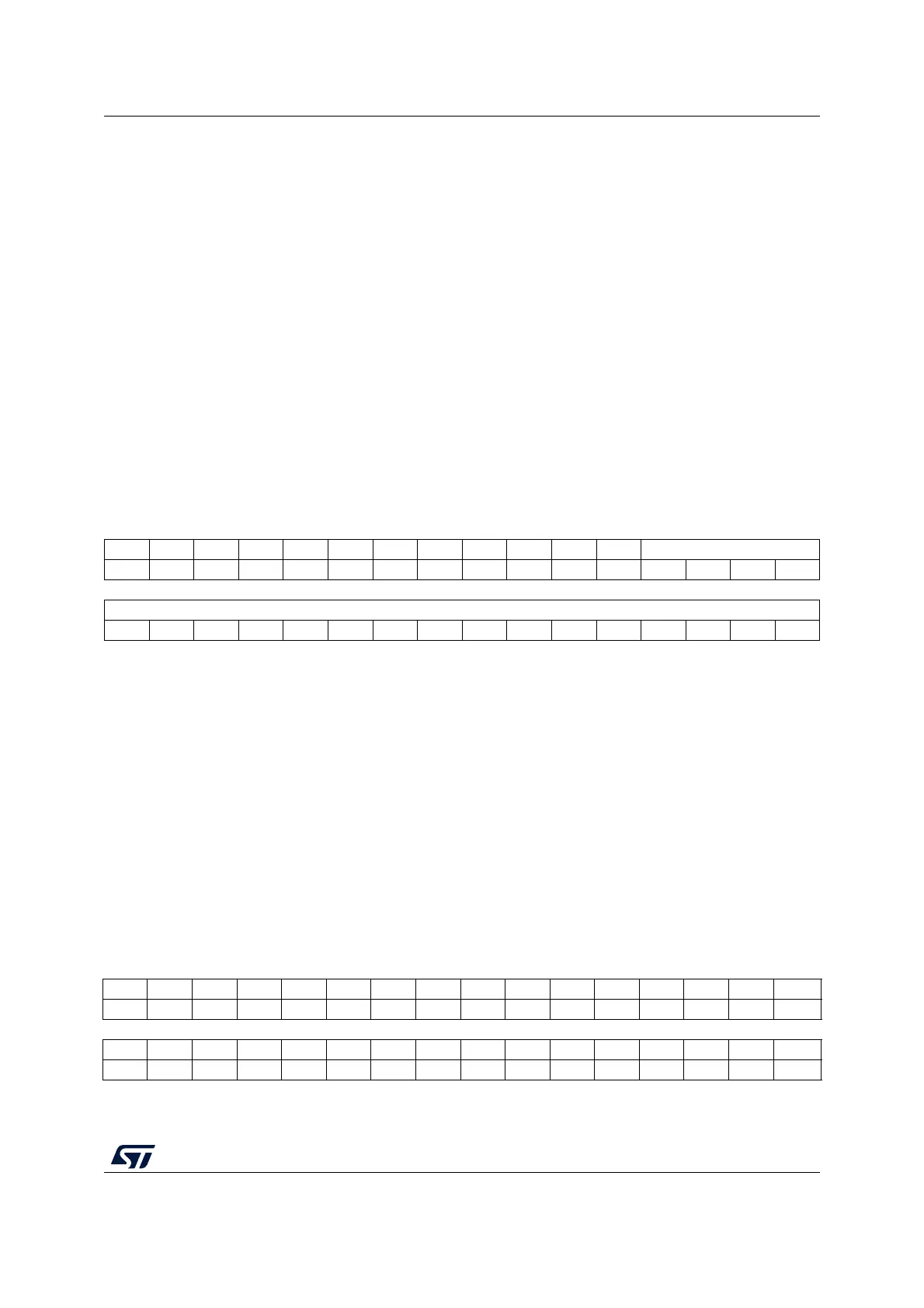

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. BRR[19:16]

rw rw rw rw

1514131211109876543210

BRR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:0 BRR[19:0]

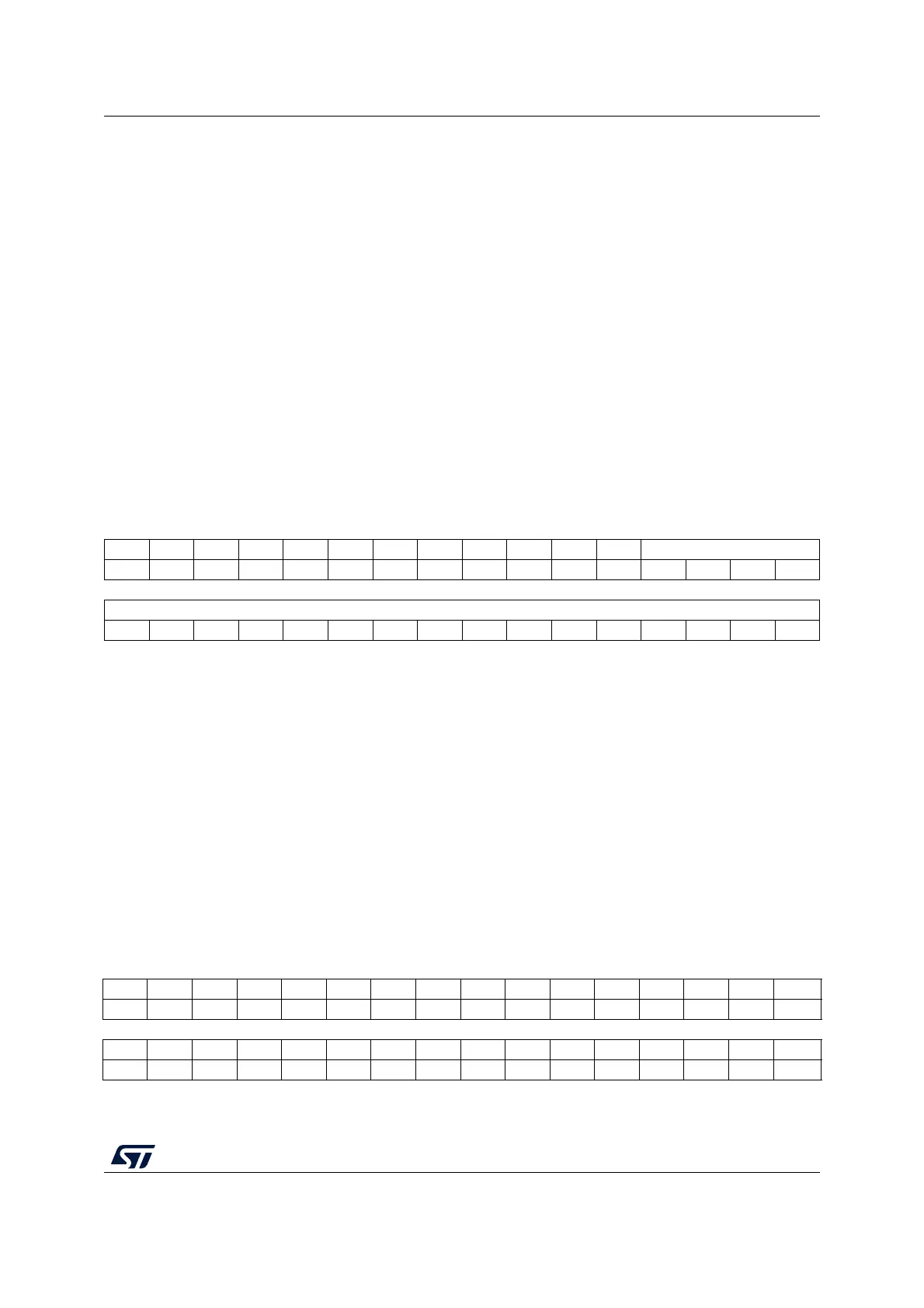

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

151413121110987654321 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RXFRQ MMRQ SBKRQ Res.

www

Loading...

Loading...