Serial peripheral interface/ inter-IC sound (SPI/I2S) RM0367

916/1043 RM0367 Rev 7

31.7.3 SPI status register (SPI_SR)

Address offset: 0x08

Reset value: 0x0002

Bit 2 SSOE: SS output enable

0: SS output is disabled in master mode and the cell can work in multimaster configuration

1: SS output is enabled in master mode and when the cell is enabled. The cell cannot work

in a multimaster environment.

Note: This bit is not used in I

2

S mode and SPI TI mode.

Bit 1 TXDMAEN: Tx buffer DMA enable

When this bit is set, the DMA request is made whenever the TXE flag is set.

0: Tx buffer DMA disabled

1: Tx buffer DMA enabled

Bit 0 RXDMAEN: Rx buffer DMA enable

When this bit is set, the DMA request is made whenever the RXNE flag is set.

0: Rx buffer DMA disabled

1: Rx buffer DMA enabled

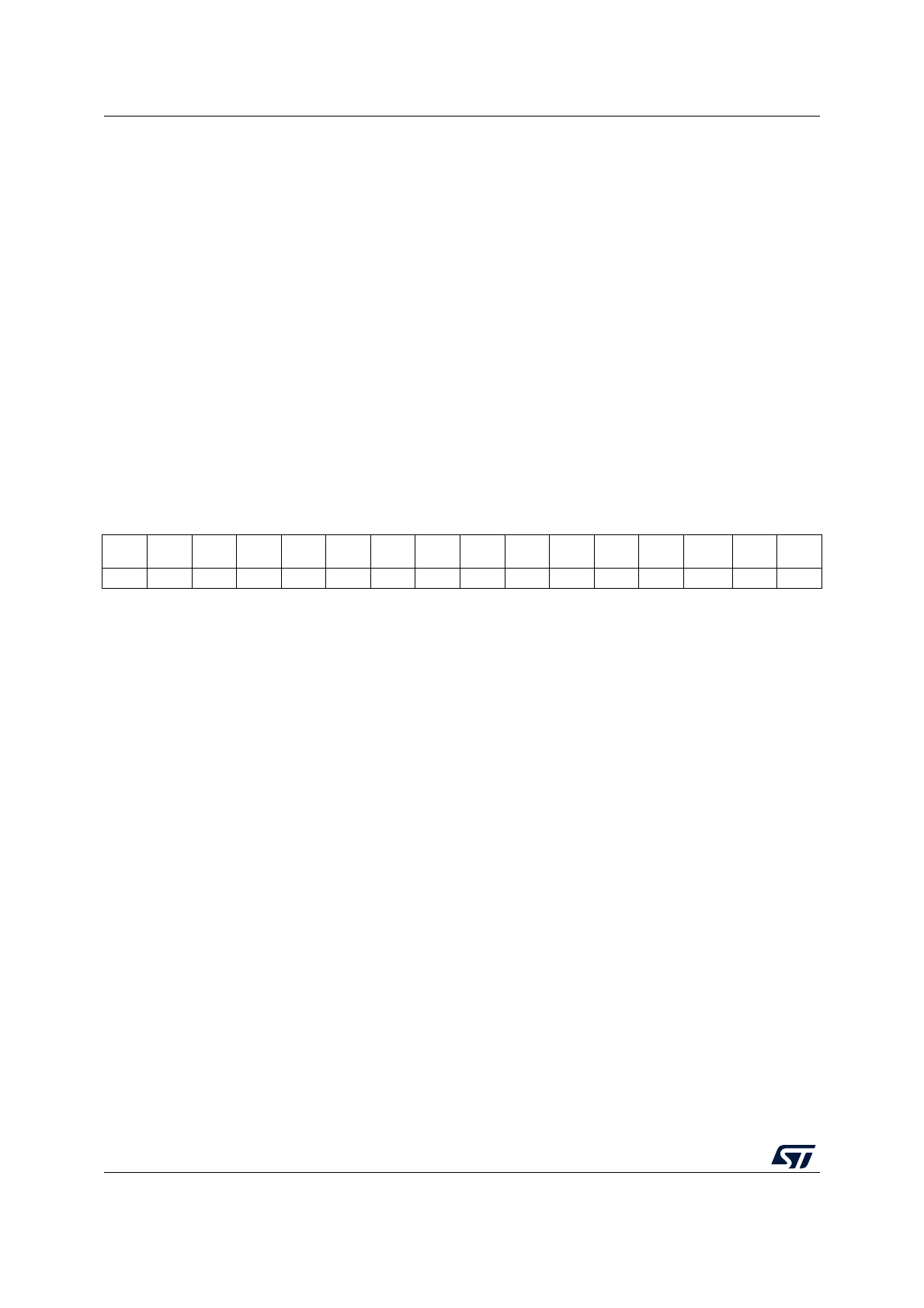

1514131211109876543 2 10

Res. Res. Res. Res. Res. Res. Res. FRE BSY OVR MODF

CRC

ERR

UDR CHSIDE TXE RXNE

rrrrrc_w0r r rr

Bits 15:9 Reserved. Forced to 0 by hardware.

Bit 8 FRE: Frame Error

0: No frame error

1: Frame error occurred.

This bit is set by hardware and cleared by software when the SPI_SR register is read.

This bit is used in SPI TI mode or in I2S mode whatever the audio protocol selected. It

detects a change on NSS or WS line which takes place in slave mode at a non expected

time, informing about a desynchronization between the external master device and the

slave.

Bit 7 BSY: Busy flag

0: SPI (or I2S) not busy

1: SPI (or I2S) is busy in communication or Tx buffer is not empty

This flag is set and cleared by hardware.

Note: BSY flag must be used with caution: refer to Section 31.3.12: SPI status flags and

Section 31.3.10: Procedure for disabling the SPI.

Bit 6 OVR: Overrun flag

0: No overrun occurred

1: Overrun occurred

This flag is set by hardware and reset by a software sequence. Refer to Section 31.3.13: SPI

error flags for the software sequence.

Loading...

Loading...