RM0367 Rev 7 967/1043

RM0367 Debug support (DBG)

970

33.9.4 Debug MCU APB1 freeze register (DBG_APB1_FZ)

The DBG_APB1_FZ register is used to configure the following APB peripherals, when the

MCU under debug:

• Timer clock counter freeze

• I2C SMBUS timeout freeze

• System window watchdog and independent watchdog counter freeze support.

This register is mapped at address 0x4001 5808.

The register is asynchronously reset by the POR (and not the system reset). It can be

written by the debugger under system reset.

Address offset:

0X08

Only 32-bit access are supported.

Power on reset (POR): 0x0000 0000 (not reset by system reset)

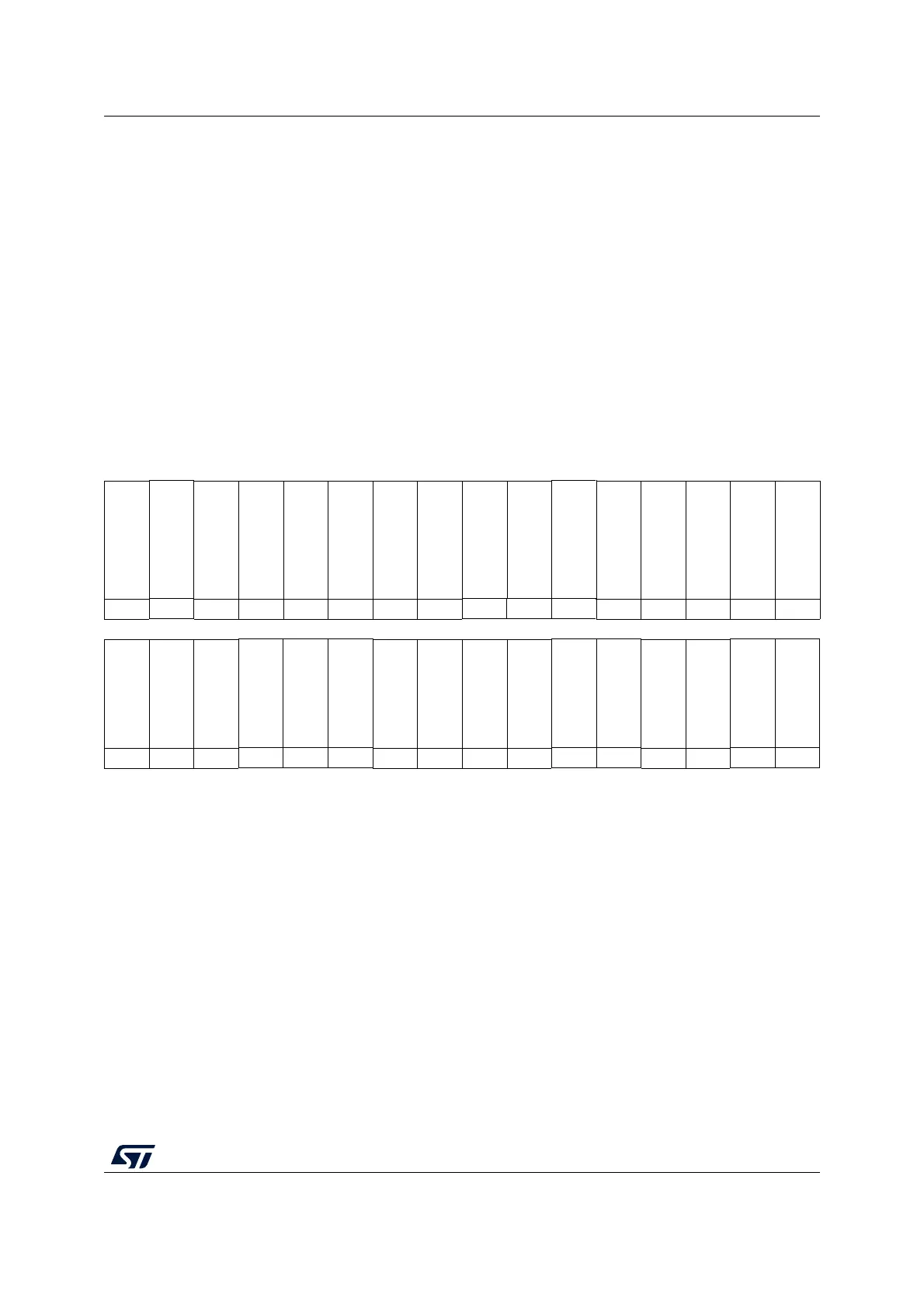

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DBG_LPTIMER_STO

P

DBG_I2C3_STOP

Res. Res. Res. Res. Res. Res. Res. Res.

DBG_I2C1_STOP

Res. Res. Res. Res. Res.

rw rw rw

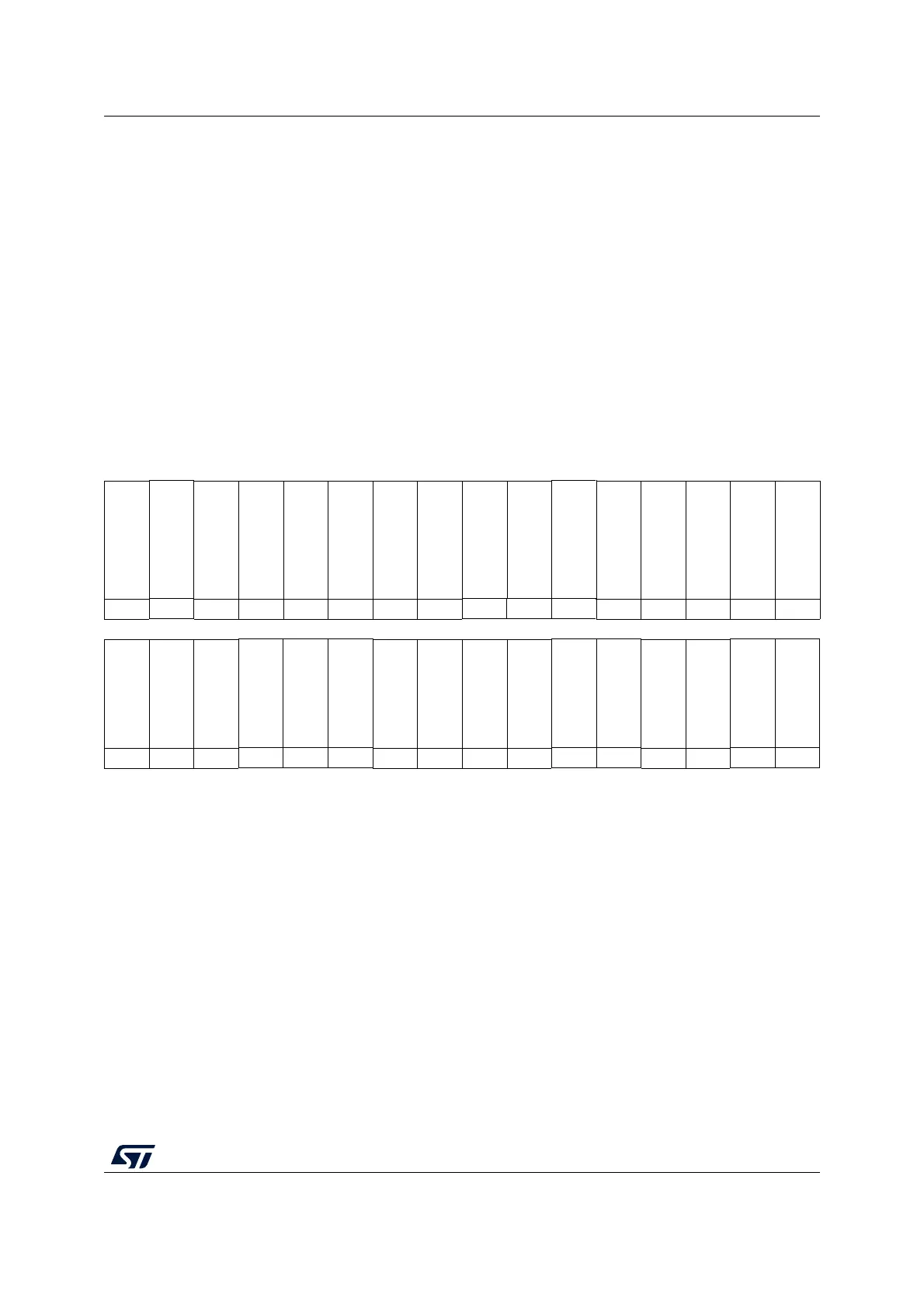

1514131211109876543210

Res. Res. Res.

DBG_IWDG_STOP

DBG_WWDG_STOP

DBG_RTC_STOP

Res. Res. Res. Res.

DBG_TIM7_STOP

DBG_TIM6_STOP

Res. Res.

.DBG_TIM3_STOP

.DBG_TIM2_STOP

rw rw rw rw rw rw rw

Bit 31 DBG_LPTIMER_STOP: LPTIM1 counter stopped when core is halted

0: LPTIM1 counter clock is fed even if the core is halted

1: LPTIM1 counter clock is stopped when the core is halted

Bit 30 DBG_I2C3_STOP: I2C3 SMBUS timeout mode stopped when core is halted

0: Same behavior as in normal mode

1: I2C3 SMBUS timeout is frozen

Bits 29:22 Reserved, must be kept at reset value.

Bit 21 DBG_I2C1_STOP: I2C1 SMBUS timeout mode stopped when core is halted

0: Same behavior as in normal mode

1: I2C1 SMBUS timeout is frozen

Bits 20:13 Reserved, must be kept at reset value.

Bit 12 DBG_IWDG_STOP: Debug independent watchdog stopped when core is halted

0: The independent watchdog counter clock continues even if the core is halted

1: The independent watchdog counter clock is stopped when the core is halted

Loading...

Loading...