Status Reporting 37

Agilent InfiniiVision 3000 X-Series Oscilloscopes Programmer's Guide 1107

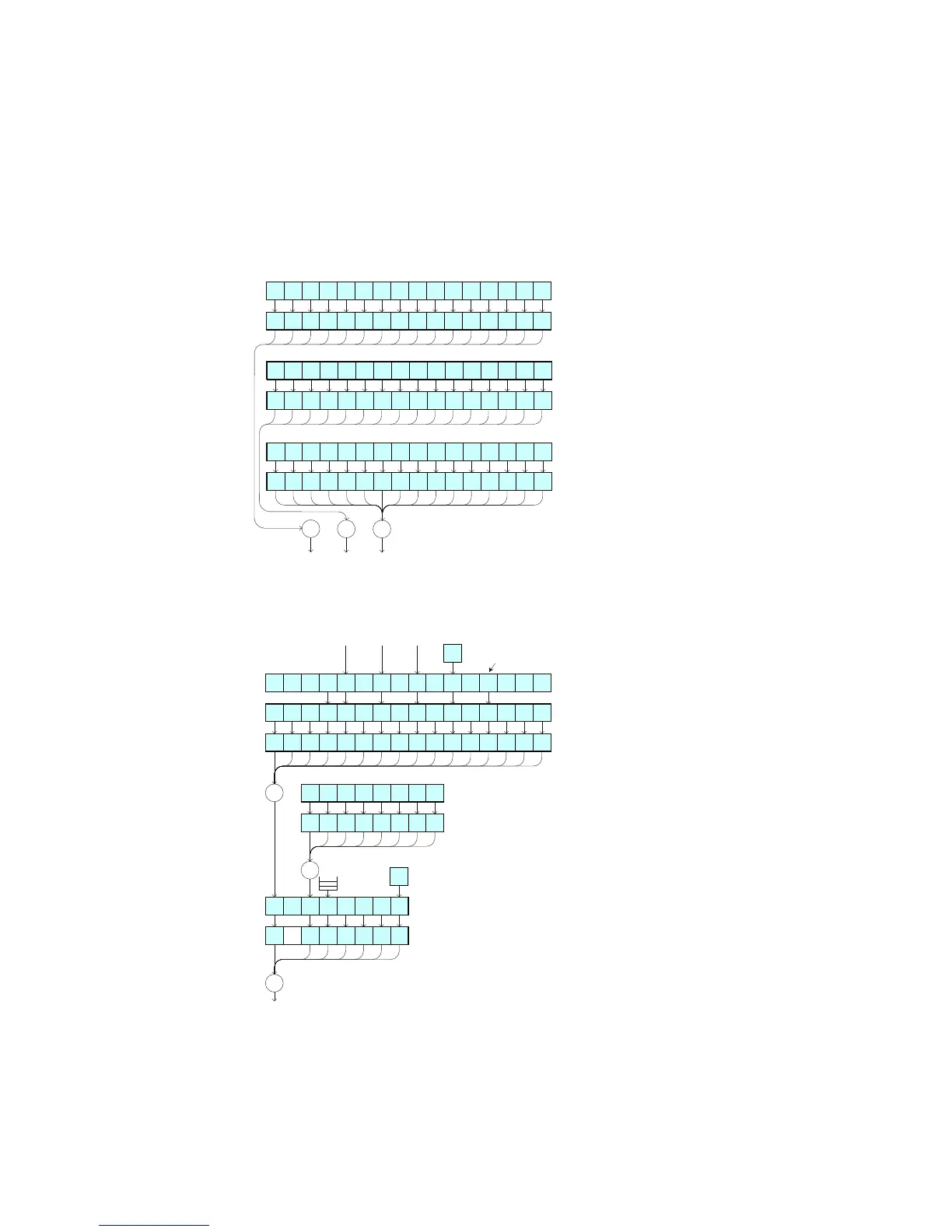

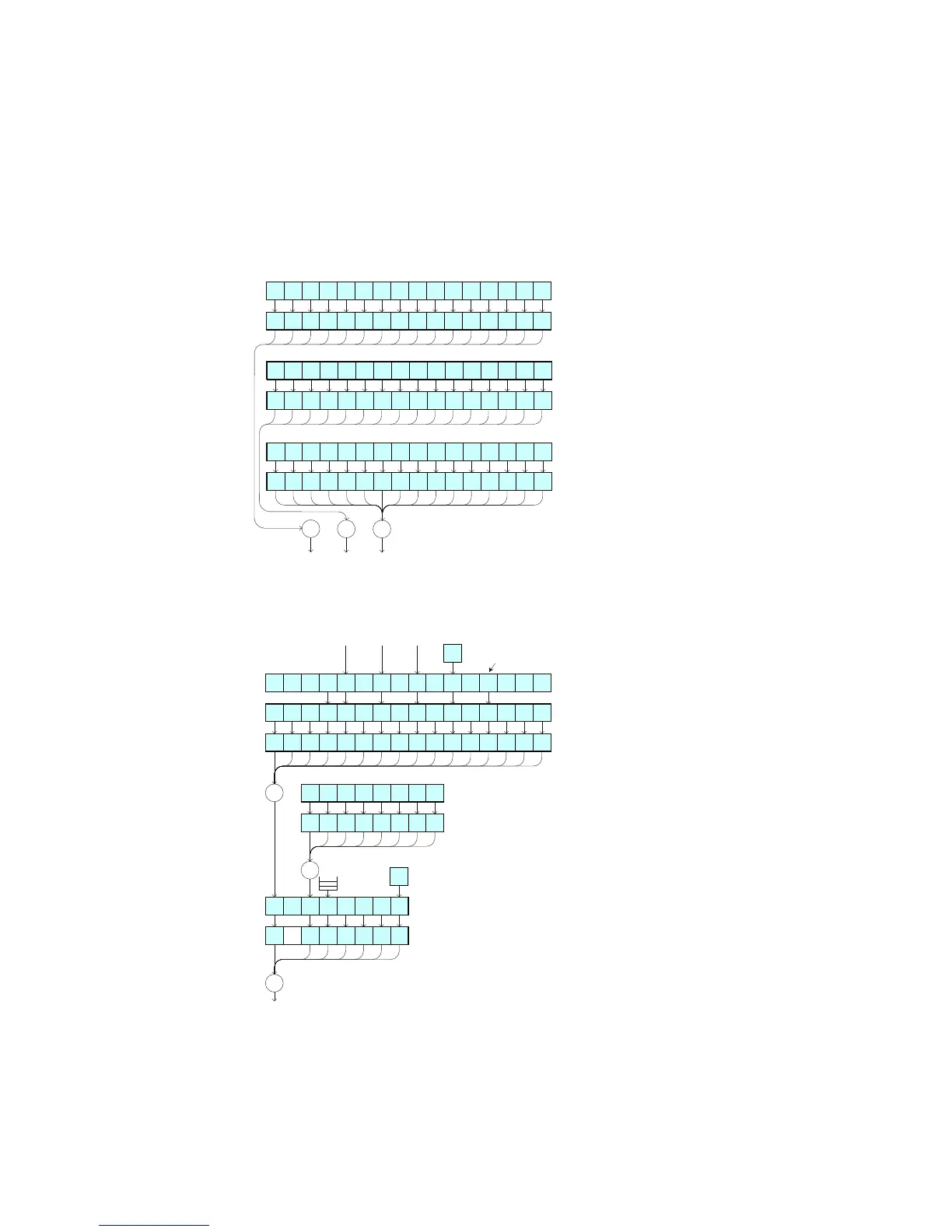

Status Reporting Data Structures

The following figure shows how the status register bits are masked and

logically OR'ed to generate service requests (SRQ) on particular events.

The status register bits are described in more detail in the following

tables:

• Table 68

OR

OR

:MTEenable

:MTEenable?

Mask Test Event Enable (MASK) Register

1023456798101112131415

:MTERegister[:EVENt]?

Mask Test Event Event Register

&RP

SOHWH

Fail

MTE

To bits in Operation Status Condition Register:

OVLR

Auto

Mask

Started

98101112131415

OR

10234567

:OVLR?

Overload Event Register

:OVL

:OVL?

Overload Event Enable (Mask) Register

Ch a n 2

OVL

Ch a n 1

OVL

Ch a n 3

OVL

Ch a n 4

OVL

Ext Trig

OVL

Ch a n 2

Fault

Ch a n 1

Fault

Ch a n 3

Fault

Ch a n 4

Fault

Ext Trig

Fault

PWR

:PWRenable

:PWRenable?

Power Event Enable (MASK) Register

1023456798101112131415

:PWRRegister[:EVENt]?

Power Event Event Register

6HWXS

Apply

De-

skew

Wai t

Trig

Ru n

Arm

Reg

AER?

Run bit set if oscilloscope not stopped

:OPERation:CONDition?

Operation Status Condition Register

:OPEE

:OPEE?

Operation Status Enable (Mask) Register

10234567

OPER TRGMAVESB

RQS /

MSS

TRG

Reg

TER?

Trigger Event Register

*SRE

*SRE?

Service Request Enable (Mask) Register

*STB?

Status Byte Register

Outp ut

Queue

SRQ

*ESR?

(Standard) Event Status Register

*ESE

*ESE?

(Standard) Event Status Enable (Mask) Register

PON URQ EXE DDE QYE RQL OPCCM E

OV LR

USR

MSG

OR

10234567

OR

1023456798101112131415

Service Request

OR

Wai t

Trig

Ru n

:OPERation[:EVENt]?

Operation Status Event Register

OV LR

11

5 3

From Overload

Event Registers

From Mask Test

Event Registers

MTE

MTE

9

7

PWR

PWR

From Power

Event Registers

Loading...

Loading...