Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 2-32

ID012310 Non-Confidential, Unrestricted Access

STREXH

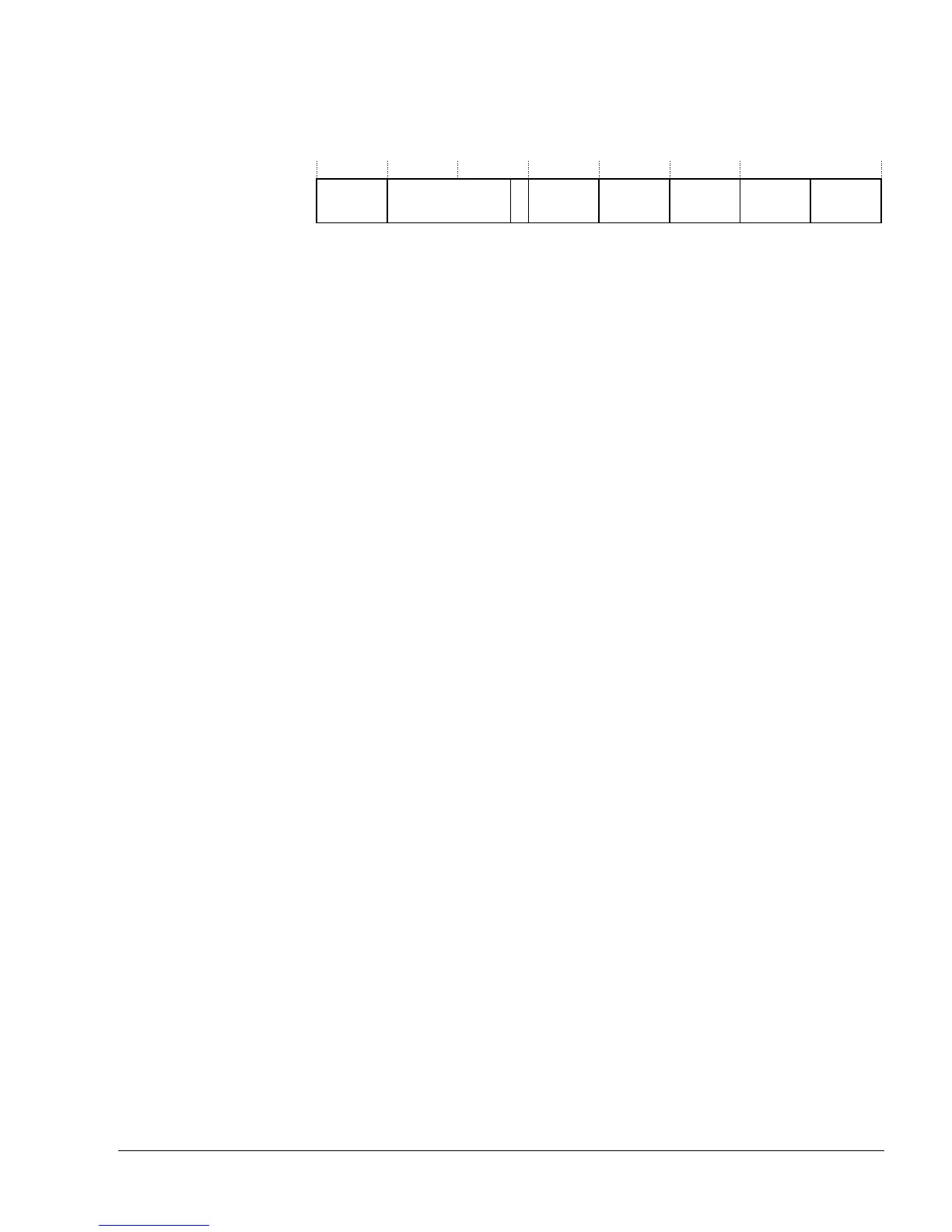

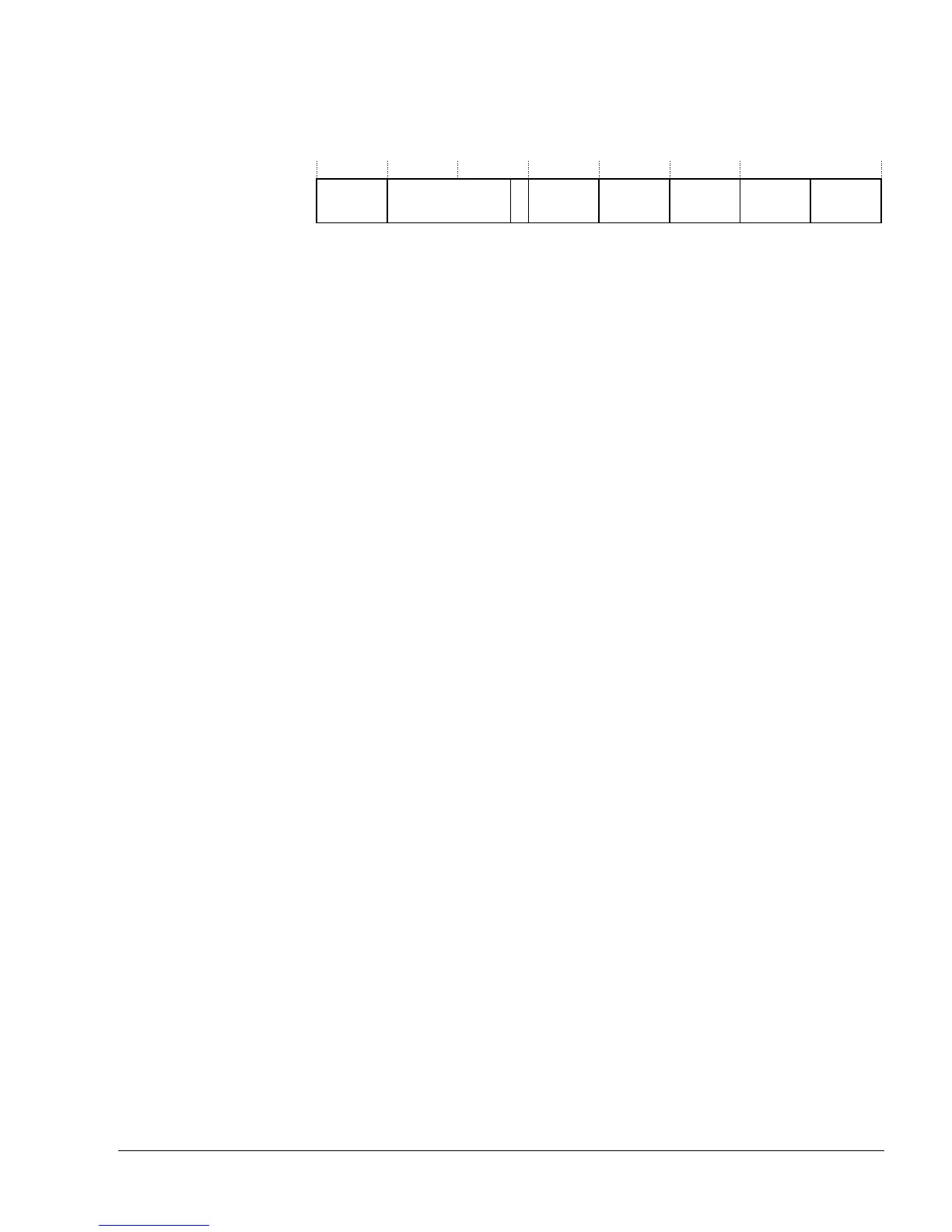

Figure 2-14 shows the format of the Store Register Halfword Exclusive, STREXH, instruction.

Figure 2-14 STREXH instruction

Syntax

STREXH{<cond>} <Rd>, <Rm>, [<Rn>]

Operation

if ConditionPassed(cond) then

processor_id = ExecutingProcessor()

if IsExclusiveLocal(processor_id) then

if Shared(Rn)==1 then

physical_address=TLB(Rn)

if IsExclusiveGlobal(physical_address,processor_id,2) then

Memory[Rn,2] = Rm

Rd = 0

ClearByAddress(physical_address,2)

else

Rd =1

else

Memory[Rn,2] = Rm

Rd = 0

else

Rd = 1

ClearExclusiveLocal(processor_id)

2.11.3 Load or Store Doubleword

The LDREXD and STREXD instructions behave as follows:

• The operands are considered as two words, that load or store to consecutive

word-addressed locations in memory.

• Register restrictions are the same as LDRD and STRD. For STRD in ARM state, the

registers Rm and R(m+1) provide the value that is stored, where m is an even number.

• The address in memory must be 64-bit aligned, address[2:0] == b000

When (A,U) == (0,1), (1,0) or (1,1) in CP15 register 1, the instruction generates alignment

faults if this condition is not met.

For more information, see Operation of unaligned accesses on page 4-13.

• The transaction must be a single access or indivisible burst on bus widths < 64 bits

For AXI based systems, the exclusive access signal, AxPROT[4], must remain asserted

throughout the burst where AxSIZE < 0x3.

The LDREXD and STREXD instructions share the same data monitors as the LDREX and

STREX instructions, a local and a global monitor for each processor, for shared memory

support.

RmCond

31 28 27 21 20 19 15 12 11 7 4 3 0

0 0 0 1 1 1 1 0 Rn Rd SBO 1 0 0 1

16 8

Loading...

Loading...