System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-3

ID012310 Non-Confidential, Unrestricted Access

Table 3-2 on page 3-14 lists the registers in the system control processor in register order and

gives their reset values.

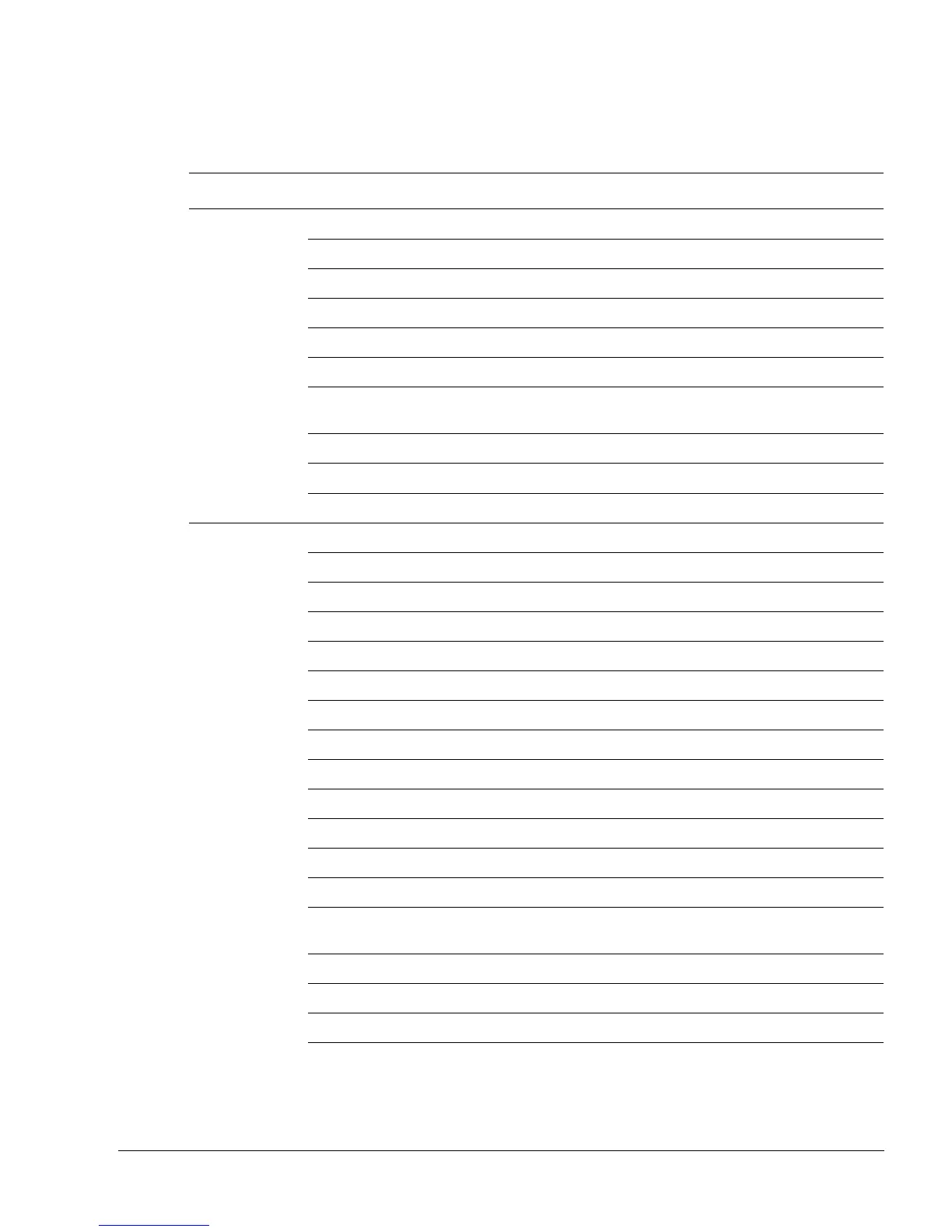

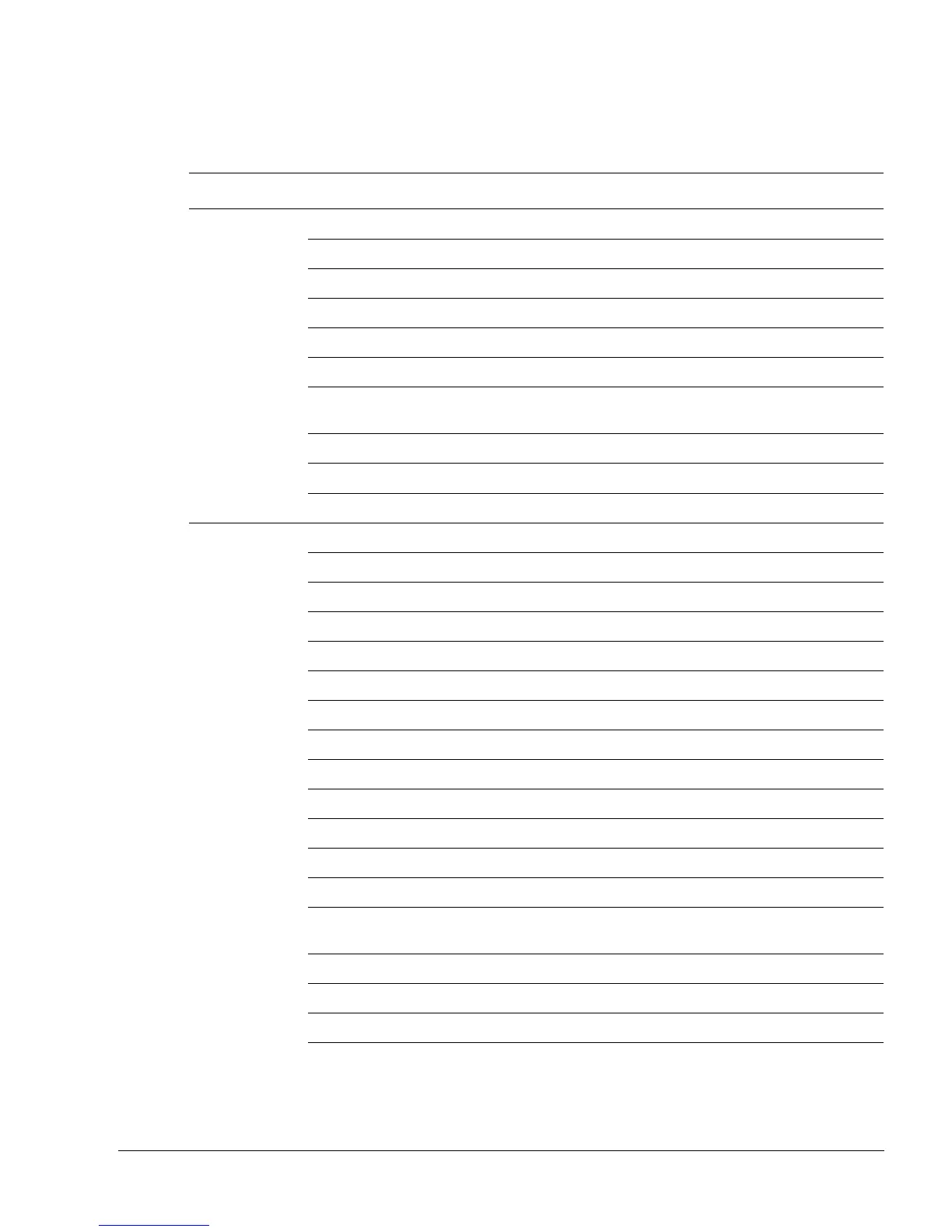

Table 3-1 System control coprocessor register functions

Function Register/operation Reference to description

System control

and configuration

Control c1, Control Register on page 3-44

Auxiliary control c1, Auxiliary Control Register on page 3-48

Secure Configuration c1, Secure Configuration Register on page 3-52

Secure Debug Enable c1, Secure Debug Enable Register on page 3-54

Non-Secure Access Control c1, Non-Secure Access Control Register on page 3-55

Coprocessor Access Control c1, Coprocessor Access Control Register on page 3-51

Secure or Non-secure Vector Base

Address

c12, Secure or Non-secure Vector Base Address Register on

page 3-121

Monitor Vector Base Address c12, Monitor Vector Base Address Register on page 3-122

ID code

a

c0, Main ID Register on page 3-20

Feature ID, CPUID scheme c0, CPUID registers on page 3-26

MMU control and

configuration

TLB Type c0, TLB Type Register on page 3-25

Translation Table Base 0 c2, Translation Table Base Register 0 on page 3-57

Translation Table Base 1 c2, Translation Table Base Register 1 on page 3-59

Translation Table Base Control c2, Translation Table Base Control Register on page 3-60

Domain Access Control c3, Domain Access Control Register on page 3-63

Data Fault Status c5, Data Fault Status Register on page 3-64

Instruction Fault Status c5, Instruction Fault Status Register on page 3-66

Fault Address c6, Fault Address Register on page 3-68

Instruction Fault Address c6, Instruction Fault Address Register on page 3-69

Watchpoint Fault Address c6, Watchpoint Fault Address Register on page 3-69

TLB Operations c8, TLB Operations Register on page 3-86

TLB Lockdown c10, TLB Lockdown Register on page 3-100

Memory Region Remap c10, Memory region remap registers on page 3-101

Peripheral Port Memory Remap c15, Peripheral Port Memory Remap Register on

page 3-130

Context ID c13, Context ID Register on page 3-128

FCSE PID c13, FCSE PID Register on page 3-126

Thread And Process ID c13, Thread and process ID registers on page 3-129

TLB Lockdown Access c15, TLB lockdown access registers on page 3-149

Loading...

Loading...