System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-102

ID012310 Non-Confidential, Unrestricted Access

Note

The behavior of the memory region remap registers depends on the TEX remap bit, see c1,

Control Register on page 3-44.

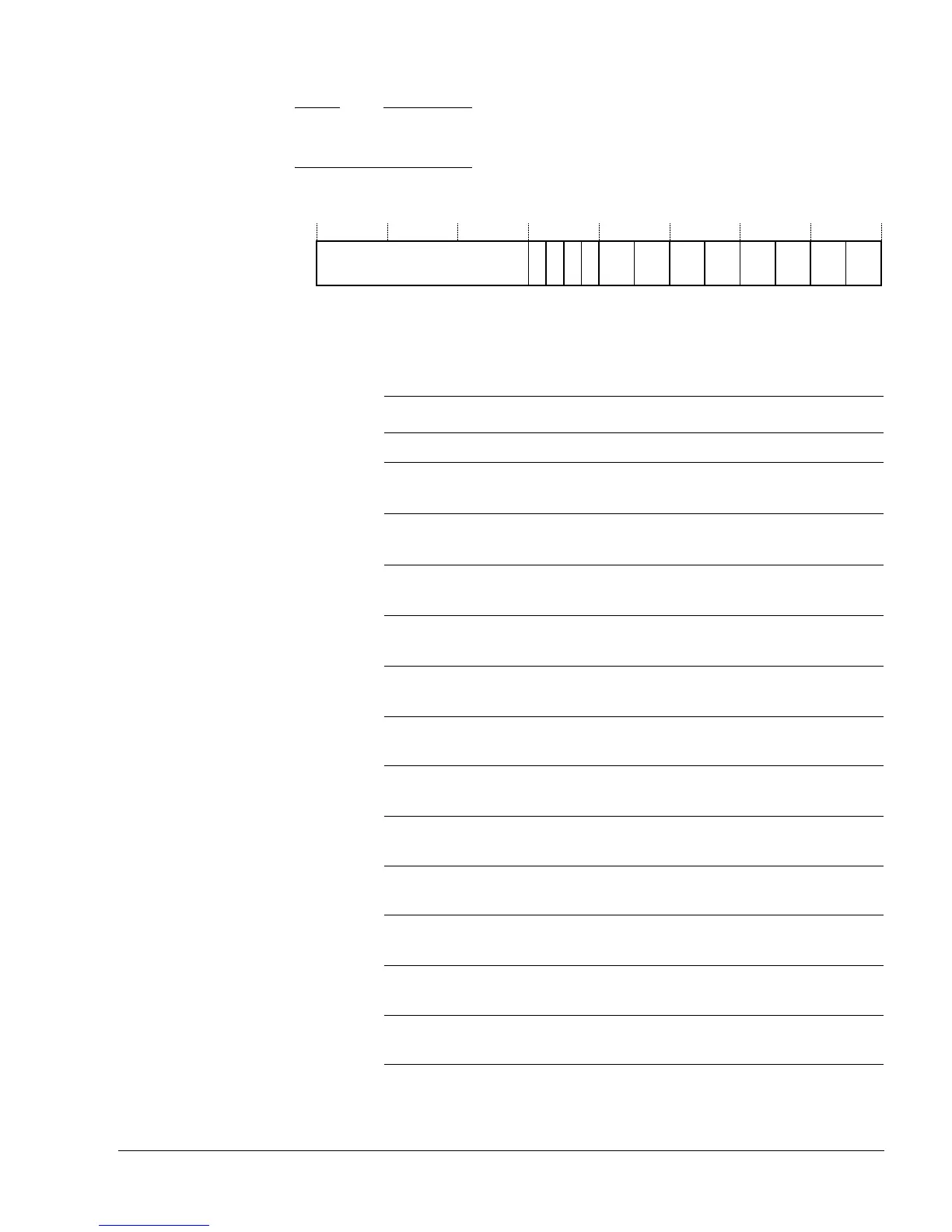

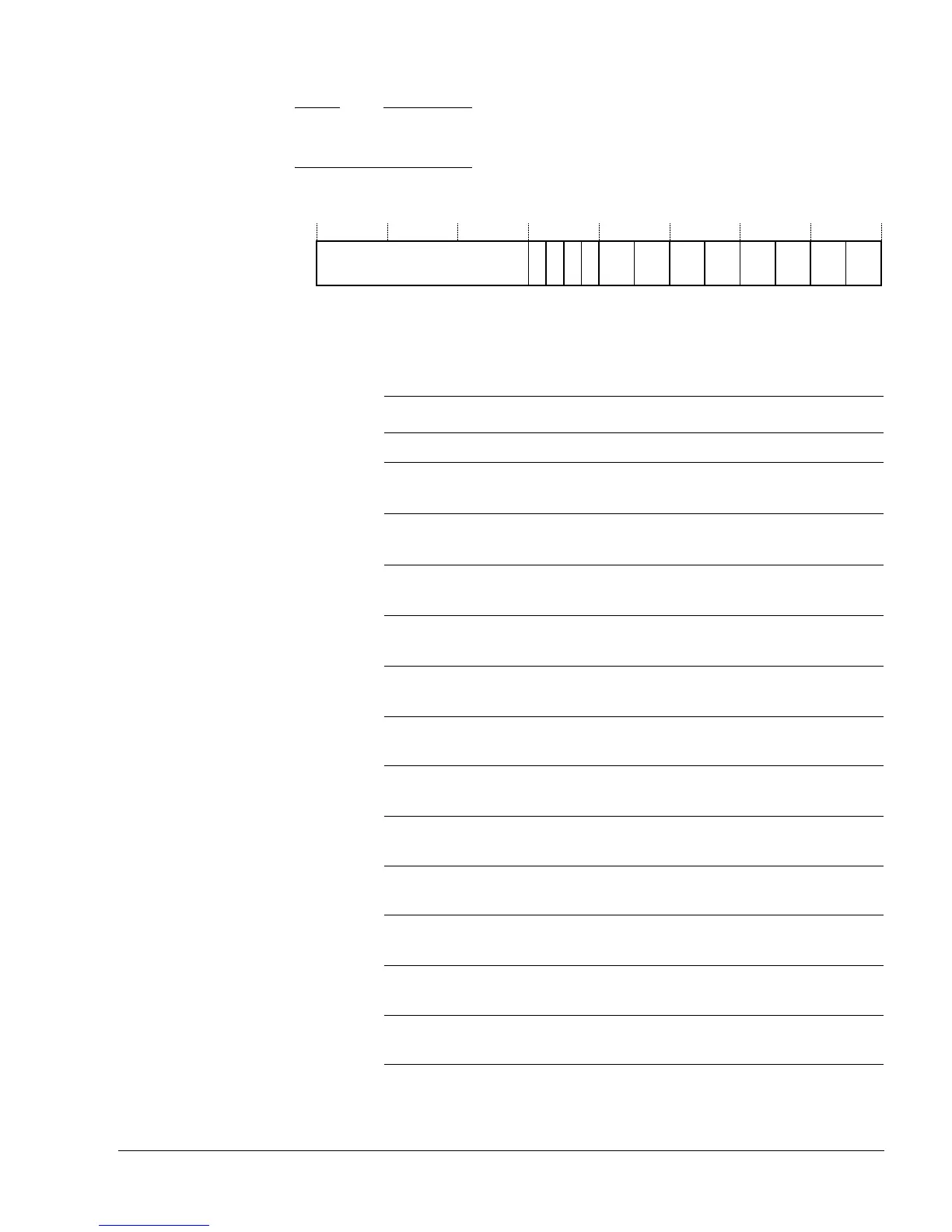

Figure 3-57 shows the arrangement of the bits in the Primary Region Remap Register.

Figure 3-57 Primary Region Remap Register format

Table 3-99 lists the functional bits of the Primary Region Remap Register.

-

31 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

UNP/SBZ - - - - - - - - - - -

Table 3-99 Primary Region Remap Register bit functions

Bits Field name

Function

a

a. The reset values ensure that no remapping occurs at reset

[31:20] - UNP/SBZ

[19] -

Remaps shareable attribute when S=1 for Normal regions

b

1 = reset value

[18] -

Remaps shareable attribute when S=0 for Normal regions

b

0 = reset value

[17] -

Remaps shareable attribute when S=1 for Device regions

b

0 = reset value

[16] -

Remaps shareable attribute when S= 0 for Device regions

b

1= reset value

[15:14] - Remaps {TEX[0],C,B} = b111

b10 = reset value

[13:12] - Remaps {TEX[0],C,B} = b110

b00 = reset value

[11:10] - Remaps {TEX[0],C,B} = b101

b10 = reset value

[9:8] - Remaps {TEX[0],C,B} = b100

b10 = reset value

[7:6] - Remaps {TEX[0],C,B} = b011

b10 = reset value

[5:4] - Remaps {TEX[0],C,B} = b010

b10 = reset value

[3:2] - Remaps {TEX[0],C,B} = b001

b01 = reset value

[1:0] - Remaps {TEX[0],C,B} = b000

b00 = reset value

Loading...

Loading...