Memory Management Unit

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 6-41

ID012310 Non-Confidential, Unrestricted Access

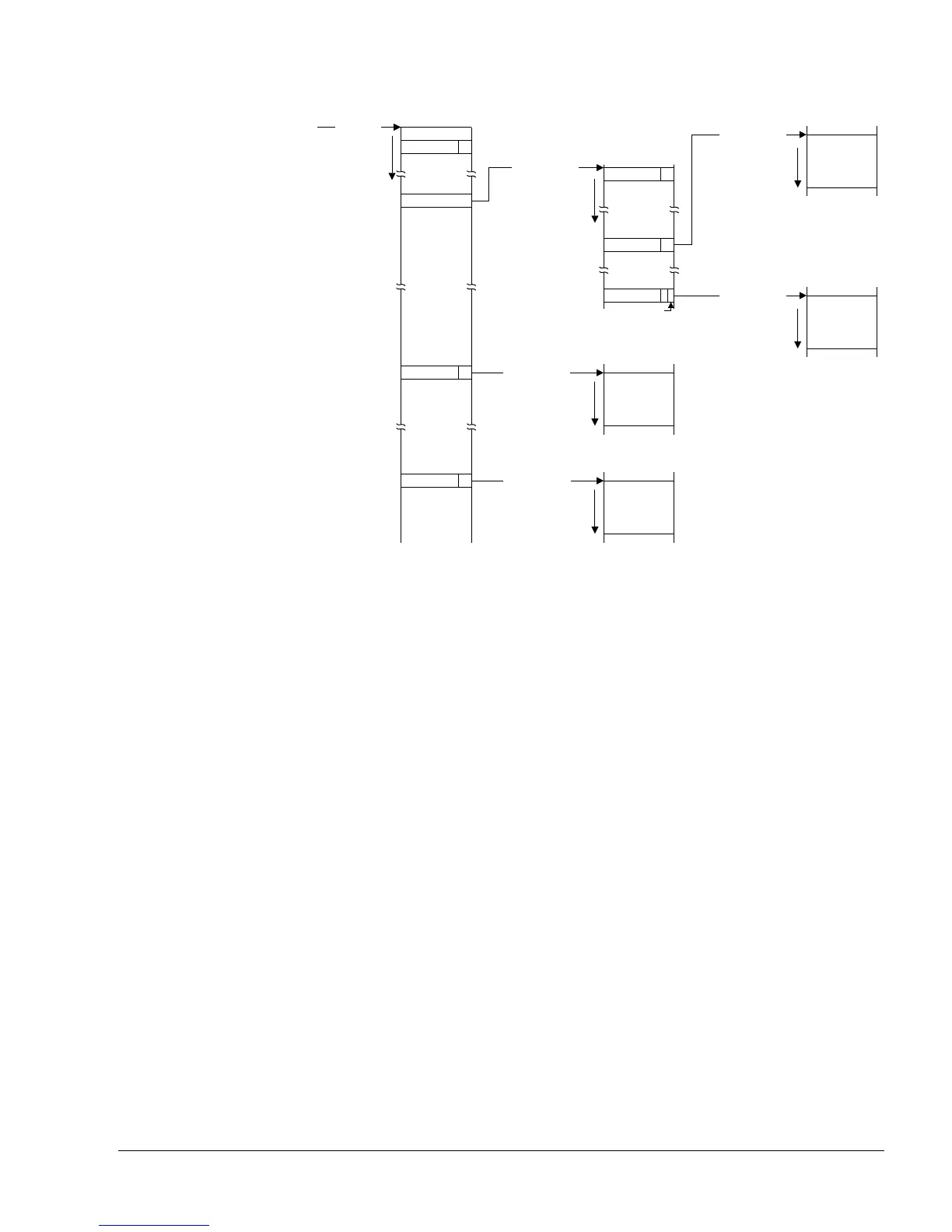

Figure 6-9 ARMv6 section, supersection, and page translation

6.11.3 Restrictions on page table mappings page coloring

The processor uses virtually indexed, physically addressed caches. To prevent alias problems

where cache sizes greater than 16KB have been implemented, you must restrict the mapping of

pages that remap virtual address bits [13:12].

• for the Instruction Cache, the Isize P bit, bit[11], of the Cache Type Register CP15 c0,

indicates if this is necessary

• for the Data Cache, the Dsize P bit, bit[23], of the Cache Type Register CP15 c0, indicates

if this is necessary.

See c0, Cache Type Register on page 3-21 for more information.

This restriction, referred to as page coloring, enables the virtual address bits[13:12] to be used

to index into the cache without requiring hardware support to avoid alias problems.

For pages marked as Non-Shared, if bit 11 or bit 23 of the Cache Type Register is set, the

restriction applies to pages that remap virtual address bits [13:12] and might cause aliasing

problems when 4KB pages are used. To prevent this you must ensure the following restrictions

are applied:

1. If multiple virtual addresses are mapped onto the same physical address then for all

mappings of bits [13:12] the virtual addresses must be equal and the same as bits [13:12]

of the physical address. The same physical address can be mapped by TLB entries of

different page sizes, including page sizes over 4KB. Imposing this requirement on the

virtual address is called page coloring.

Invalid

Invalid

01

Indexed by

VA[19:12]

Base address

from L2D[31:12]

Indexed by

VA[11:0]

Indexed by

VA[15:0]

Base address

from L2D[31:16]

First level

page table

Coarse page

table

4KB extended

small page

64KB large page

Translation

table base

Indexed by

VA[31:20]

31 0

31 0

31 0

Base address

from L1D[31:24]

Indexed by

VA[23:0]

16MB

supersection

Base address

from L1D[31:20]

Indexed by

VA[19:0]

1MB section

Base address

from L1D[31:10]

01

00

00

(bit 18 = 0) 10

(bit 18 = 1) 10

1

XN

Loading...

Loading...