The VFP Register File

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 19-3

ID012310 Non-Confidential, Unrestricted Access

19.2 Register file internal formats

The VFPv2 architecture provides the option of an internal data format that is different from

some or all of the external formats. In this implementation of the VFP11 coprocessor, data in

the register file has the same format as data in memory. Load or store operations for

single-precision, double-precision, or integer data do not modify the format as a consequence of

the transfer. However, to ensure compatibility with future VFP implementations, use

FLDMX/FSTMX instructions when saving context and restoring VFP11 registers. See section

C5 of the ARM Architecture Reference Manual for more information.

It is the responsibility of the programmer to be aware of the data type in each register. The

hardware does not perform any checking of the agreement between the data type in the source

registers and the data type expected by the instruction. Hardware always interprets the data

according to the precision implied in the instruction.

Accessing a register that has not been initialized or loaded with valid data is Unpredictable. A

way to detect access to an uninitialized register is to load all registers with Signaling NaNs

(SNaNs) in the precision of the initial access of the register and enable the Invalid Operation

exception.

19.2.1 Integer data format

The VFP11 coprocessor supports signed and unsigned 32-bit integers. Signed integers are

treated as two’s complement values. No modification to the data is implicit in a load, store, or

transfer operation on integer data. The format of integer data within the register file is identical

to the format in memory or in an ARM11 general-purpose register.

19.2.2 Single-precision data format

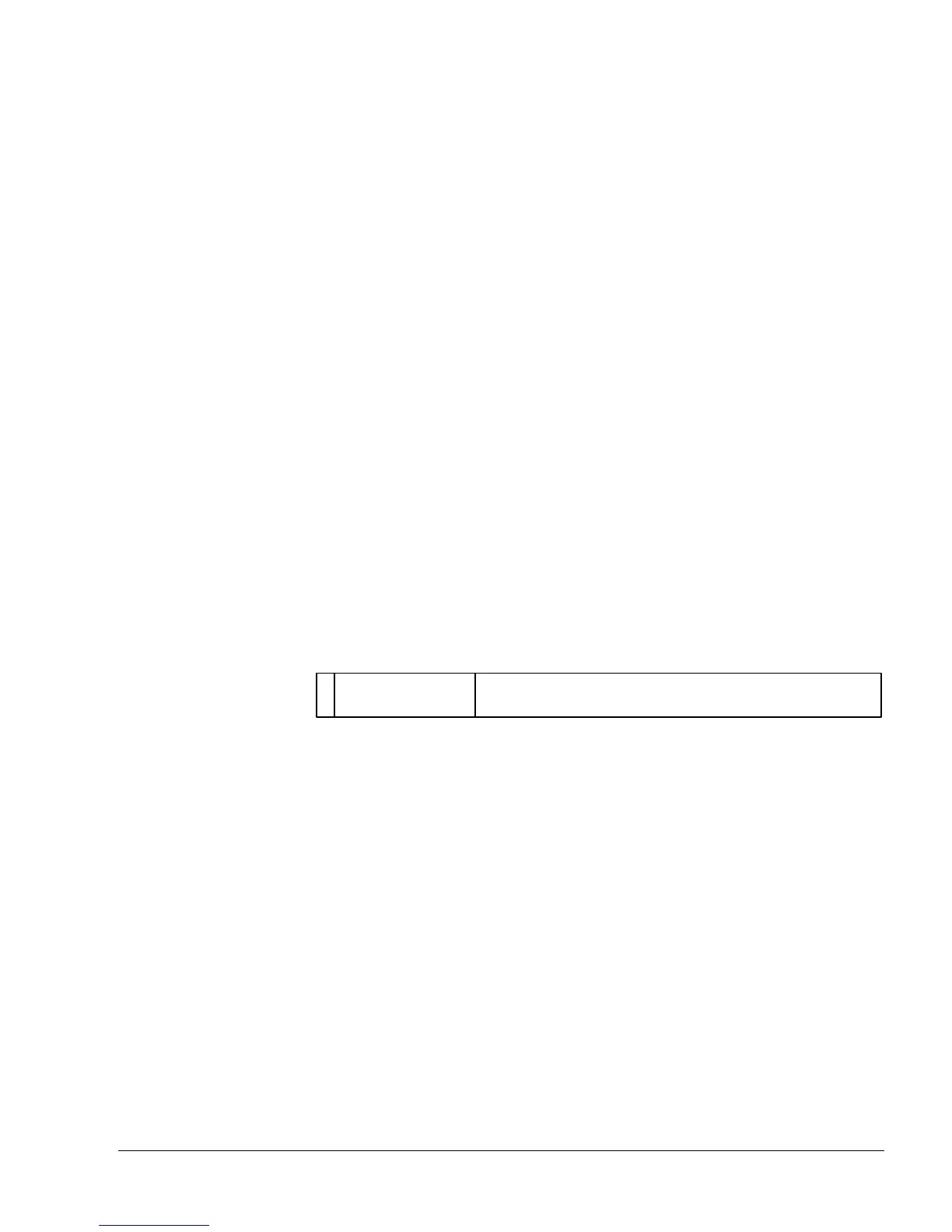

Figure 19-1 shows the single-precision bit fields.

Figure 19-1 Single-precision data format

The single-precision data format contains:

• the sign bit, bit [31]

• the exponent, bits [30:23]

• the fraction, bits [22:0].

The IEEE 754 standard defines the single-precision data format of the VFP11 coprocessor. See

the IEEE 754 standard for details about exponent bias, special formats, and numerical ranges.

19.2.3 Double-precision data format

Double-precision format has a Most Significant Word (MSW) and a Least Significant Word

(LSW). Figure 19-2 on page 19-4 shows the double-precision bit fields.

31

FractionS Exponent

22 030 23

Loading...

Loading...