VFP Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 20-13

ID012310 Non-Confidential, Unrestricted Access

Table 20-4 lists the ARM11 processor modes for accessing the VFP11 system registers.

Table 20-4 shows that a privileged ARM11 mode is sometimes required to access a VFP11

system register. When a privileged mode is required, an instruction that tries to access a register

in a nonprivileged mode takes the Undefined Instruction trap.

The following sections describe the VFP11 system registers:

• Floating-Point System ID Register, FPSID

• Floating-Point Status and Control Register, FPSCR on page 20-14

• Floating-point exception register, FPEXC on page 20-16

• Instruction registers, FPINST and FPINST2 on page 20-18.

20.4.1 Floating-Point System ID Register, FPSID

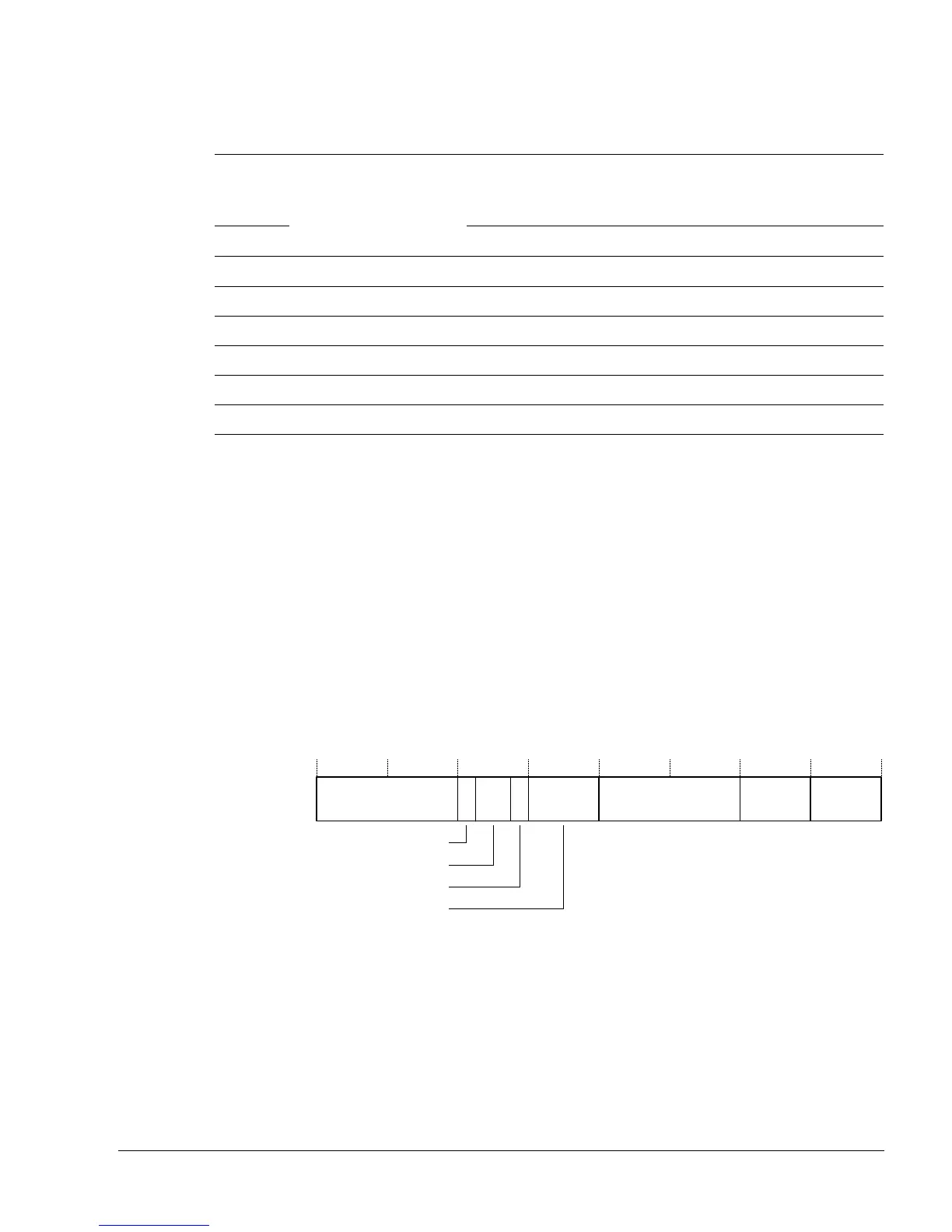

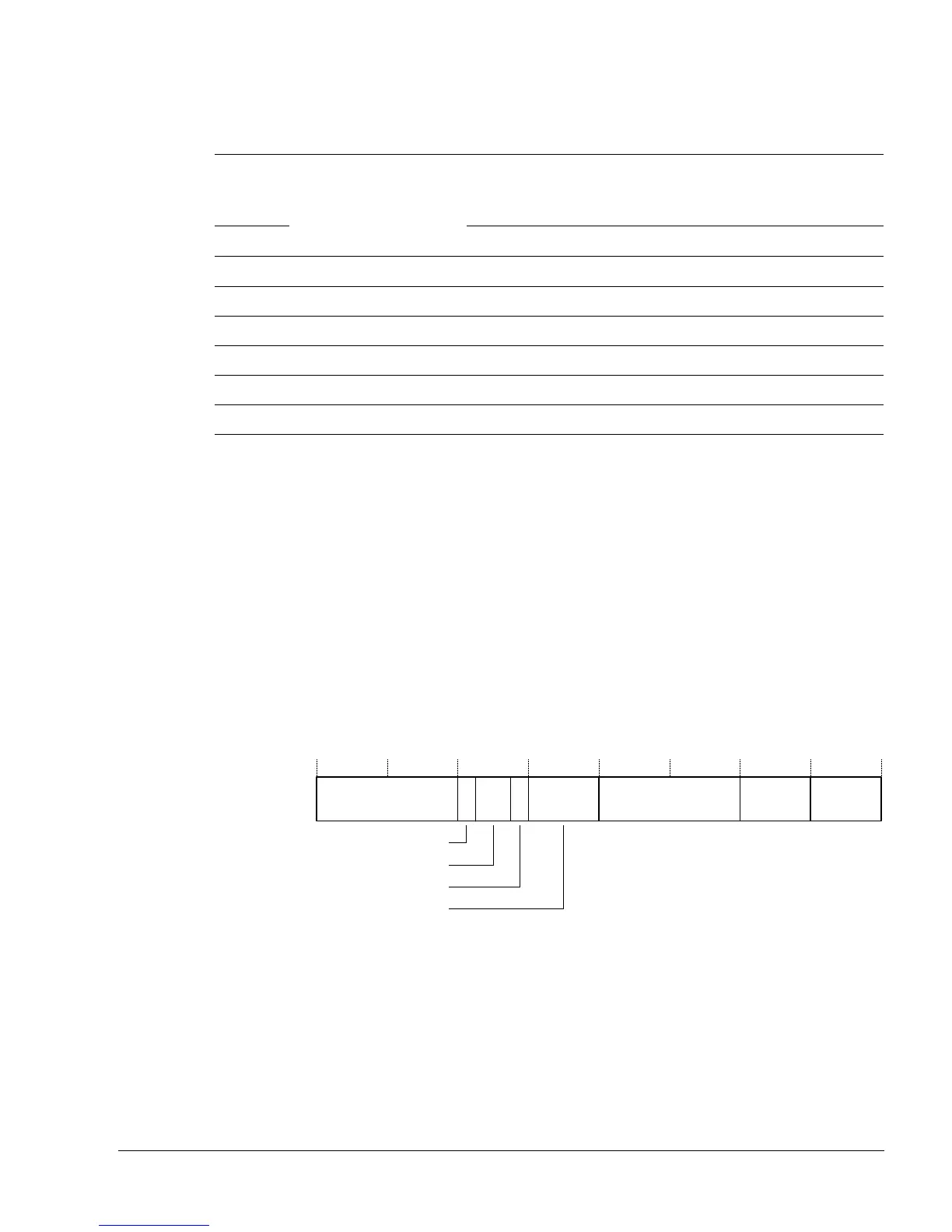

FPSID is a read-only register that identifies the VFP11 coprocessor. Figure 20-5 shows the

FPSID bit fields.

Figure 20-5 Floating-Point System ID Register

Table 20-4 Accessing VFP11 system registers

FMXR/FMRX <reg> field

ARM11 processor mode

Register VFP11 coprocessor enabled VFP11 coprocessor disabled

FPSID b0000 Any mode Privileged mode

FPSCR b0001 Any mode

None

a

FPEXC b1000 Privileged mode Privileged mode

FPINST b1001 Privileged mode Privileged mode

FPINST2 b1010 Privileged mode Privileged mode

MVFR0 b0111 Any mode Privileged mode

MVFR1 b0110 Any mode Privileged mode

a. An instruction that tries to access FPSCR while the VFP11 coprocessor is disabled takes the Undefined Instruction trap.

SW

Format

SNG

Architecture

Variant Revision

31 20 16 15 8 7 4 3 024 23 192122

Implementer

Part number

Loading...

Loading...