Memory Management Unit

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 6-15

ID012310 Non-Confidential, Unrestricted Access

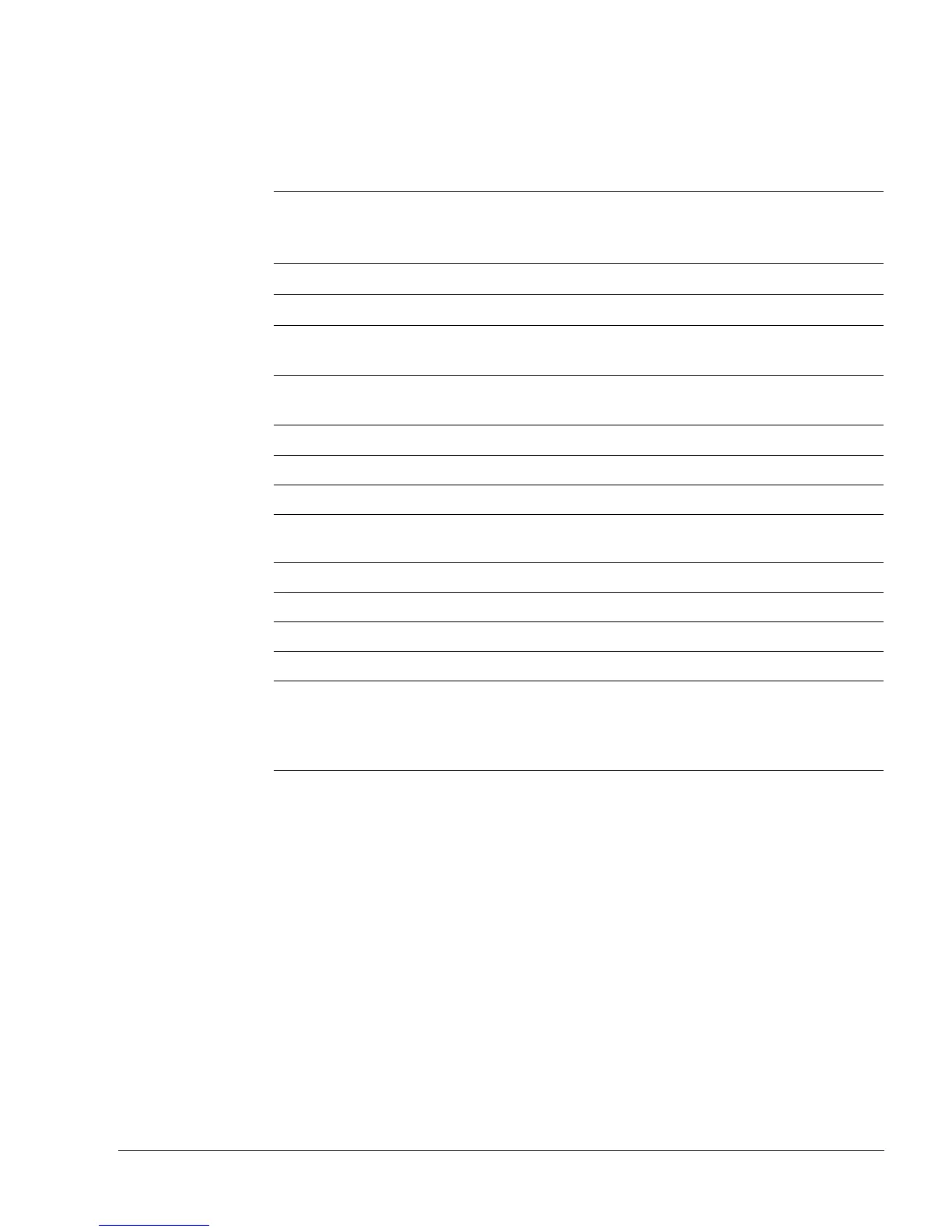

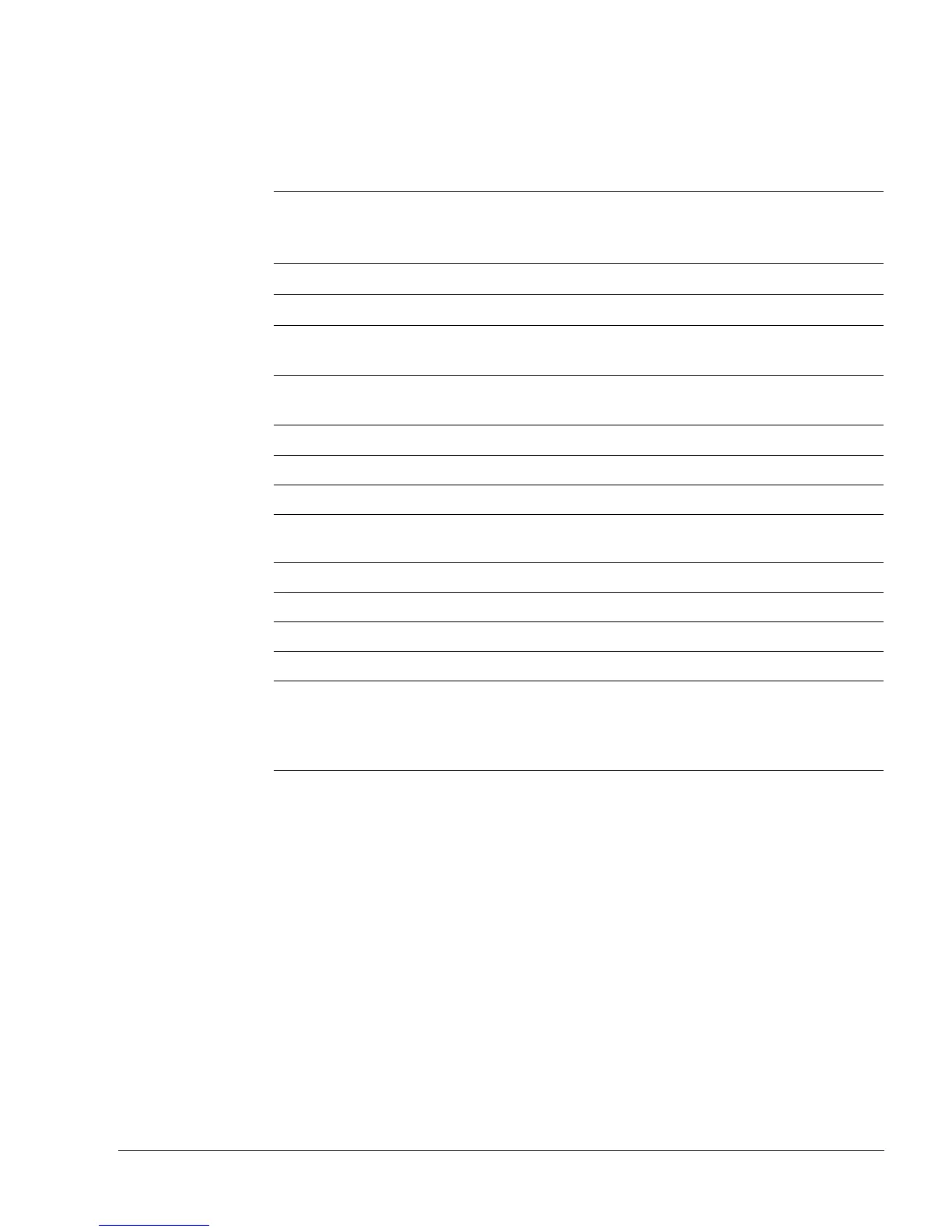

The S bit in the descriptors only applies to Normal, that is not Device and not Strongly Ordered

memory. Table 6-2 summarizes the TEX[2:0], C, and B encodings used in the page table

formats, and the value of the shareable attribute of the concerned page:

The Inner and Outer cache policy bits control the operation of memory accesses to the external

memory:

• The C and B bits are described as the AA bits and define the Inner cache policy

• The TEX[1:0] bits are described as the BB bits and define the Outer cache policy.

Table 6-2 TEX field, and C and B bit encodings used in page table formats

Page table encodings

Description Memory type Page shareable?

TEX C B

b000 0 0 Strongly Ordered Strongly Ordered

Shared

a

a. Shared, regardless of the value of the S bit in the page table.

b000 0 1 Shared Device Device

Shared

a

b000 1 0 Outer and Inner Write-Through,

No Allocate on Write

Normal

s

b

b. s is Shared if the value of the S bit in the page table is 1, or Non-shared if the value of the S bit is 0 or not

present.

b000 1 1 Outer and Inner Write-Back,

No Allocate on Write

Normal

s

b

b001 0 0 Outer and Inner Noncacheable Normal

s

b

b001 0 1 Reserved - -

b001 1 0 Reserved - -

b001 1 1 Outer and Inner Write-Back,

Allocate on Write

c

c. The cache does not implement allocate on write.

Normal

s

b

b010 0 0 Non-Shared Device Device Non-shared

b010 0 1 Reserved - -

010 1 X Reserved - -

011 X X Reserved - -

1BB A A Cached memory.

BB = Outer policy,

AA = Inner policy.

See Table 6-3 on page 6-16.

Normal

s

b

Loading...

Loading...