System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-9

ID012310 Non-Confidential, Unrestricted Access

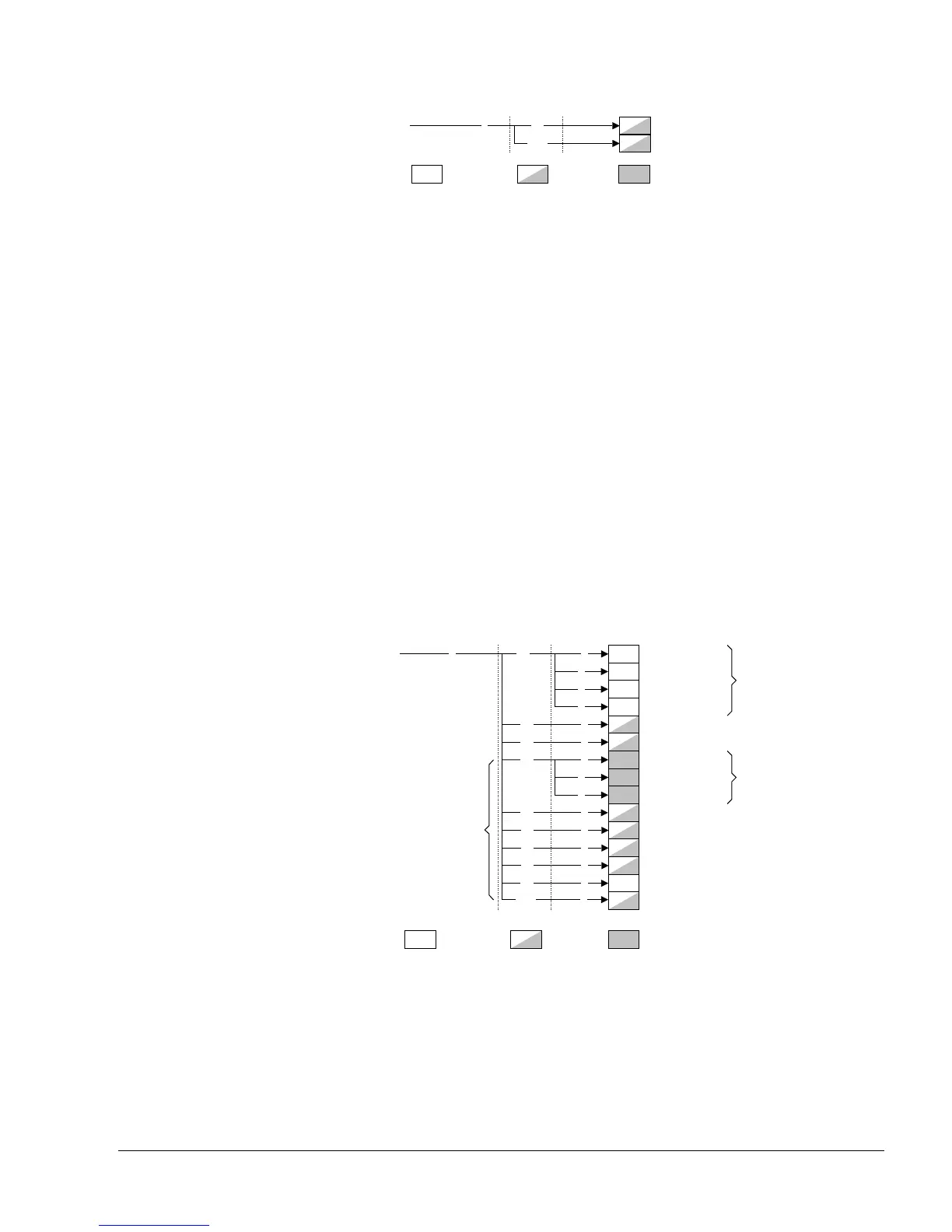

Figure 3-5 Cache Master Valid Registers

To use the Cache Master Valid Registers you read or write the individual registers that make up

the group, see Use of the system control coprocessor on page 3-12.

The Cache Master Valid Registers behave as a set of bits that define the cache contents as valid

or invalid. The number of bits is a function of the cache size.

3.1.7 DMA control

The purpose of the DMA control registers is to:

• enable software to control DMA

• transfer large blocks of data between the TCM and an external memory

• determine accessibility

• select DMA channel.

The Enable, Control, Internal Start Address, External Start Address, Internal End Address,

Channel Status, and Context ID Registers are multiple registers with one register of each for

each channel that is implemented.

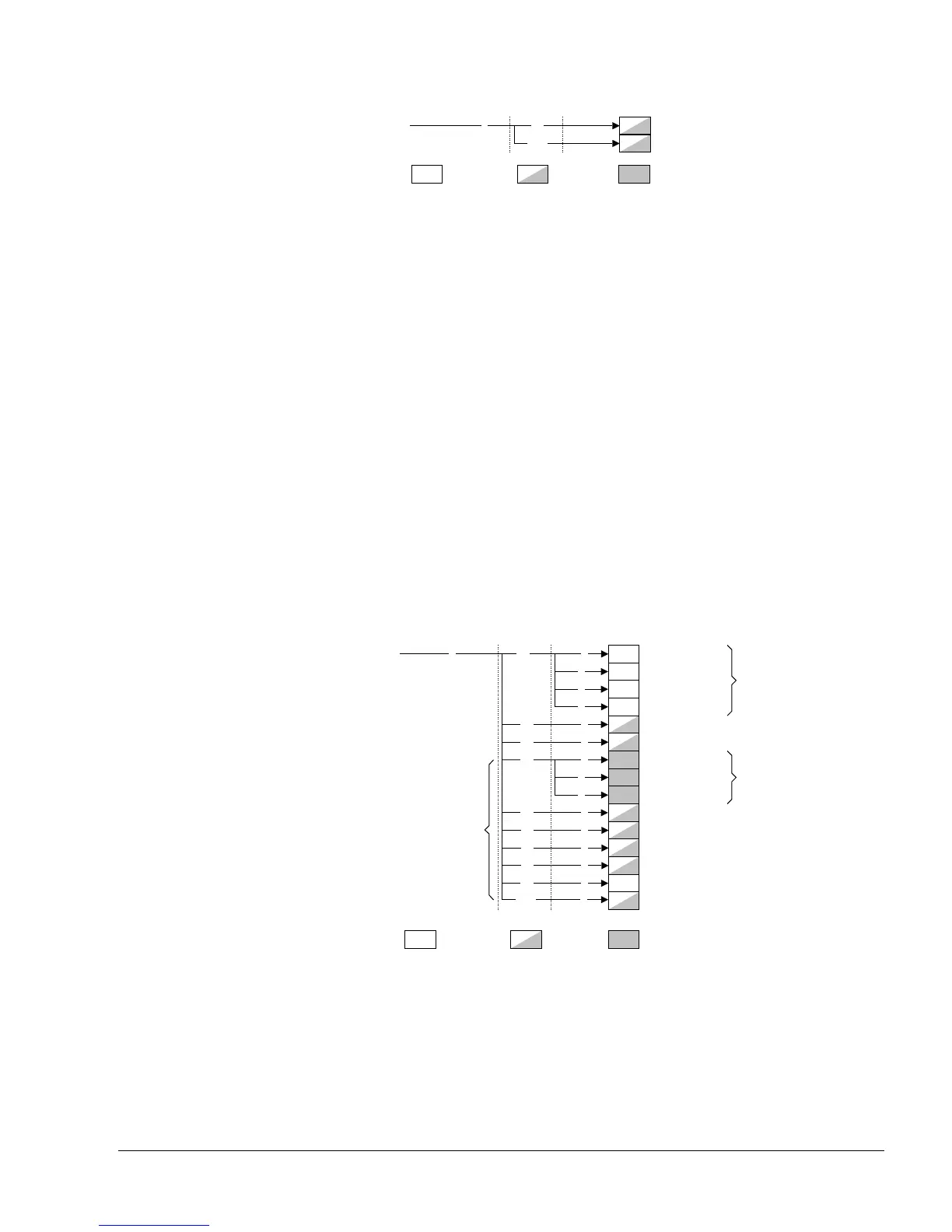

The DMA control registers consist of five 32-bit read-only registers, three 32-bit write-only

registers and seven 32-bit read/write registers. Figure 3-6 shows the arrangement of registers.

Figure 3-6 DMA control and configuration registers

To use the DMA control and configuration registers you read or write the individual registers

that make up the group, see Use of the system control coprocessor on page 3-12.

Code can execute several DMA operations while in User mode if these operations are enabled

by the DMA User Accessibility Register.

If DMA control registers attempt to execute a privileged operation in User mode the processor

takes an Undefined instruction trap.

c15

Data Cache Master Valid Register

Instruction Cache Master Valid Registerc8

c12

Read-only Read/write

3

CRn CRmOpcode_1 Opcode_2

Write-only Accessible in User mode

Write-onlyRead-only Read/write

DMA Context ID Register

One register per channel selected

by DMA Channel Number Register

c11

c0

DMA Internal End Address Register

DMA Channel Status Register

DMA External Start Address Register

DMA Internal Start Address Register

DMA Enable

Registers

Present

DMA User Accessibility Register

DMA Channel Number Register

DMA Control Register

DMA Identification

and Status Registers

Queued

Running

Interrupting

Stop

Start

Clear

c3

c2

c1

c4

c5

c6

c7

c8

3

1

2

2

1

0

0

0

0

0

0

0

0

0

0

c15

0

Opcode_2Opcode_1 CRmCRn

Accessible in User mode

Loading...

Loading...