Debug

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 13-36

ID012310 Non-Confidential, Unrestricted Access

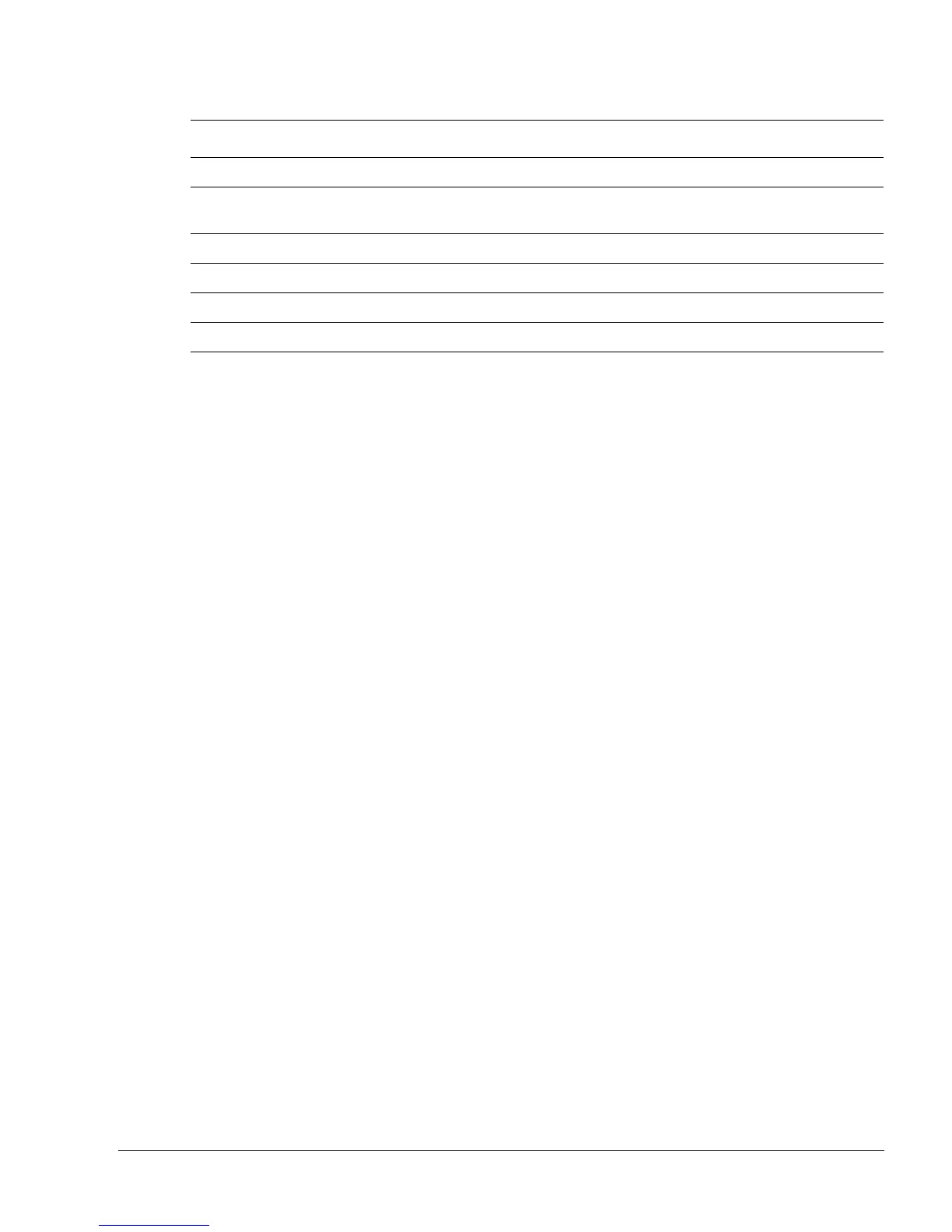

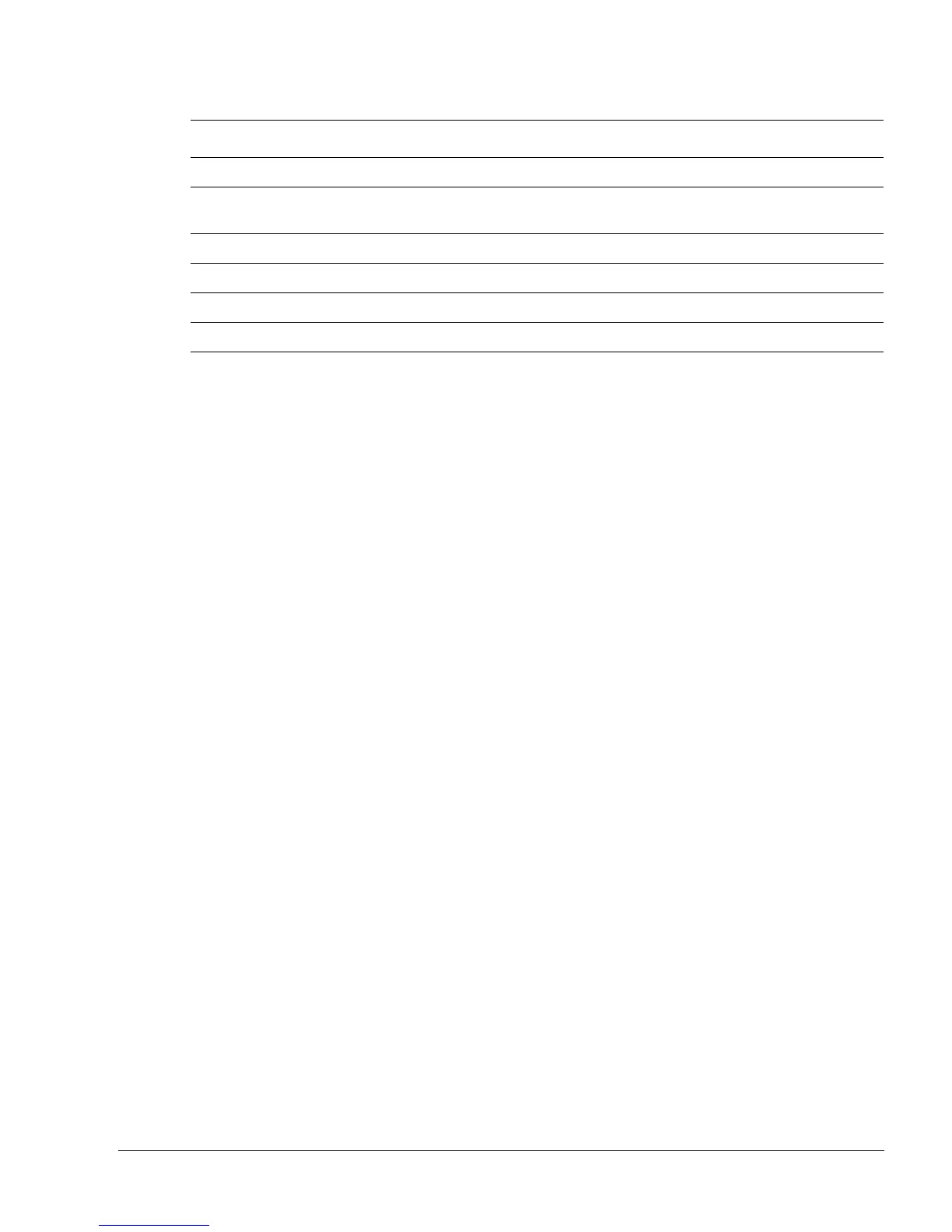

Table 13-24 Values in the link register after exceptions

Cause of fault ARM Thumb Jazelle

Return address (RA

a

) meaning

Breakpoint RA+4 RA+4 RA+4 Breakpointed instruction address

Watchpoint RA+8 RA+8 RA+8 Address of the instruction where the execution resumes, a number

of instructions after the one that hit the watchpoint

BKPT instruction RA+4 RA+4 RA+4 BKPT instruction address

Vector catch RA+4 RA+4 RA+4 Vector address

Prefetch Abort RA+4 RA+4 RA+4 Address of the instruction where the execution resumes

Data Abort RA+8 RA+8 RA+8 Address of the instruction where the execution resumes

a. This is the address of the instruction that the processor first executes on Debug state exit. Watchpoints can be imprecise.

RA is not the address of the instruction immediately after the one that hit the watchpoint, the processor might stop a number of

instructions later. The address of the instruction that hit the watchpoint is in the CP15 WFAR.

Loading...

Loading...