VFP Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 20-14

ID012310 Non-Confidential, Unrestricted Access

Table 20-5 lists the FPSID bit fields.

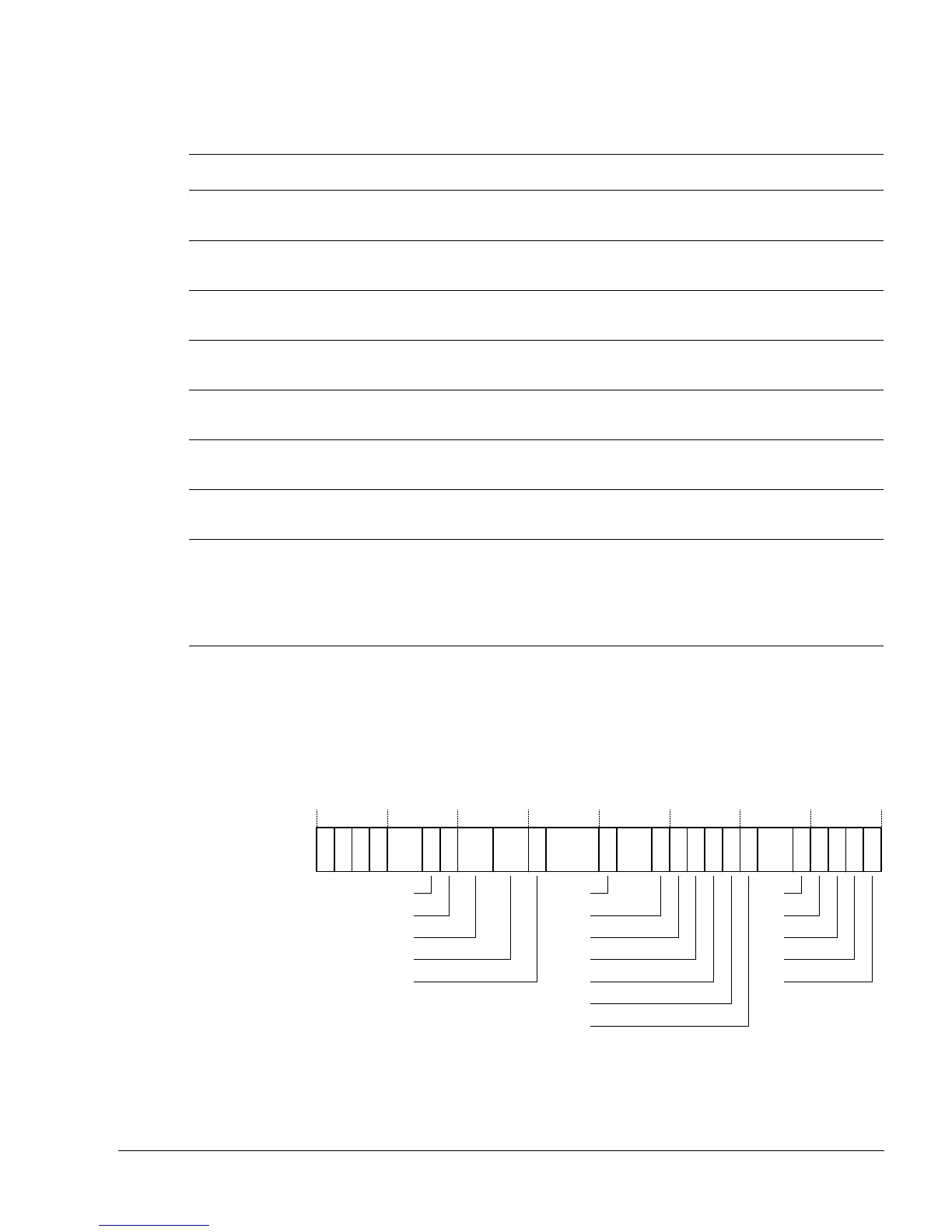

20.4.2 Floating-Point Status and Control Register, FPSCR

FPSCR is a read/write register that can be accessed in both privileged and unprivileged modes.

All bits that Figure 20-6 describes as SBZ are reserved for future expansion. They must be

initialized to zeros. To ensure that these bits are not modified, code other than initialization code

must use read/modify/write techniques when writing to FPSCR. Failure to observe this rule can

cause Unpredictable results in future systems. Figure 20-6 shows the FPSCR bit fields.

Figure 20-6 Floating-Point Status and Control Register

Table 20-5 FPSID bit fields

Bit Meaning Value

[31:24] Implementer

0x41

A, ARM Limited

[23] Hardware/software 0

Hardware implementation

[22:21] FSTMX/FLDMX

format

b00

Format 1

[20] Precisions supported 0

Both single-precision and double-precision data supported

[19:16] Architecture version b0001

VFPv2 architecture

[15:8] Part number

0x20

VFP11

[7:4] Variant

0xB

ARM11 VFP coprocessor

[3:0] Revision Incremented on each revision of the VFP11 coprocessor. Values for the ARM11JZF-S

product releases are:

ARM1176JZF-S r0p0:

0x3

ARM1176JZF-S r0p1 and r0p2: 0x4

ARM1176JZF-S r0p4 and r0p6: 0x5

31 30 29 28 25 24 23 22 21 20 19 15 12 11 10 9 8 7 4 3 2 1 0

IXC

IDC

SBZ

DZE

IOE

UFE

OFE

SBZ

IXE

IDE

LEN

Rmode

Stride

SBZ

SBZ

DN

FZ

NZCV

UFC

OFC

DZC

IOC

27 26 18 16 14 13 6 5

Loading...

Loading...