Debug

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 13-6

ID012310 Non-Confidential, Unrestricted Access

Note

All the debug resources required for Monitor debug-mode debugging are accessible through

CP14 registers. For Halting debug-mode debugging some additional resources are required. See

Chapter 14 Debug Test Access Port.

13.3.2 CP14 c0, Debug ID Register (DIDR)

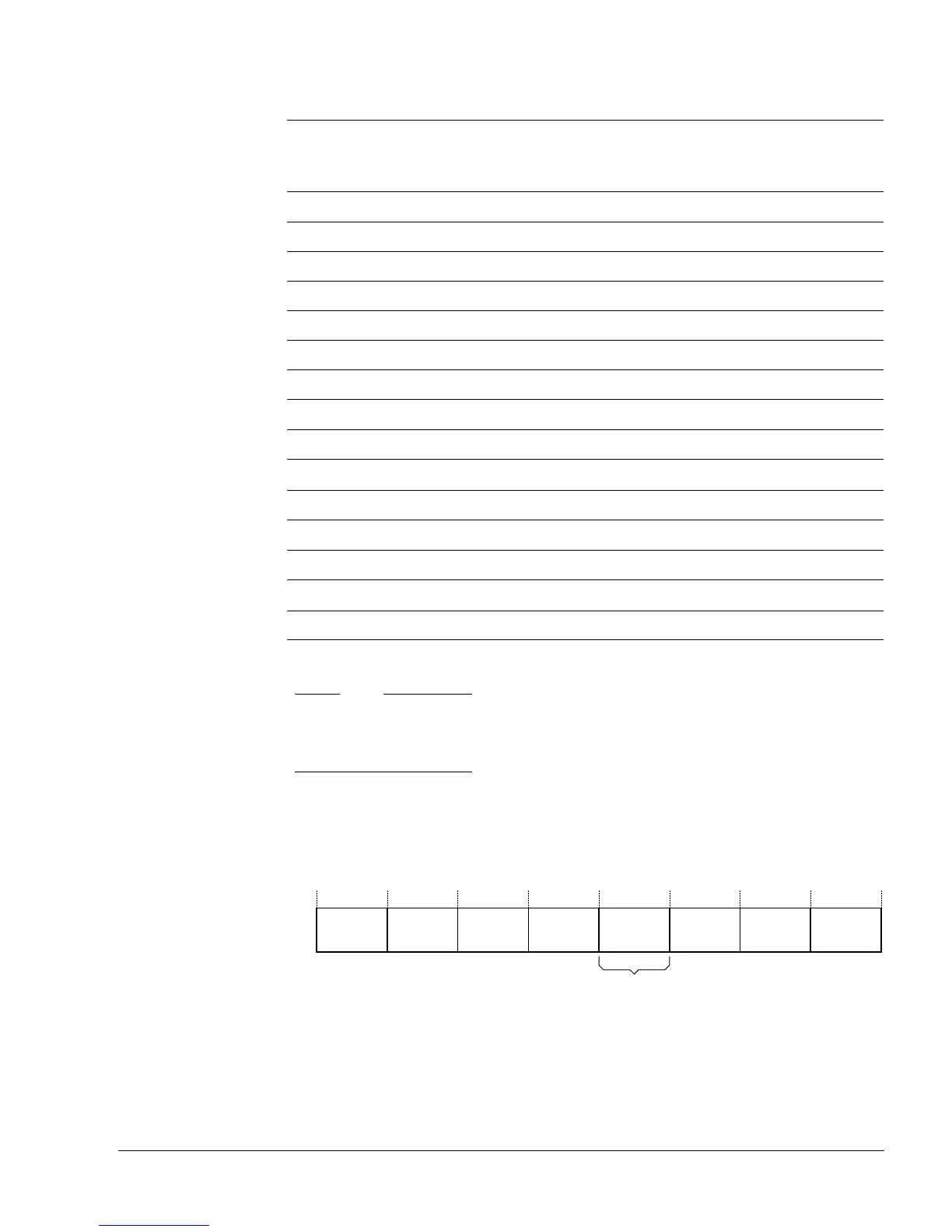

The Debug ID Register is a read-only register that defines the configuration of debug registers

in a system. Figure 13-2 shows the format of the Debug ID Register.

Figure 13-2 Debug ID Register format

For the ARM1176JZF-S processor:

• DIDR[31:8] has the value 0x15121x

b000 b0110 c6 Watchpoint Fault Address Register WFAR

b000 b0111 c7 Vector Catch Register VCR

b000 b1000-b1001 c8-c9 Reserved -

b000 b1010 c10 Debug State Cache Control Register DSCCR

b000 b1011 c11 Debug State MMU Control Register DSMCR

b000 b1100-b1111 c12-c15 Reserved -

b001-b011 b0000-b1111 c16-c63 Reserved -

b100 b0000-b0101 c64-c69 Breakpoint Value Registers

BVRy

a

b0110-b111 c70-c79 Reserved -

b101 b0000-b0101 c80-c85 Breakpoint Control Registers

BCRy

a

b0110-b1111 c86-c95 Reserved -

b110 b0000-b0001 c96-c97 Watchpoint Value Registers

WVRy

a

b0010-b1111 c98-c111 Reserved -

b111 b0000-b0001 c112-c113 Watchpoint Control Registers

WCRy

a

b0010-b1111 c114-c127 Reserved -

a. y is the decimal representation for the binary number CRm.

Table 13-2 CP14 debug register map (continued)

Binary address

Register

number

CP14 debug register name Abbreviation

Opcode_2 CRm

WRP

31 28 27 24 23 20 19 16 15 8 7 4 3 0

BRP Context Version UNP/SBZ Variant Revision

12 11

Debug architecture revision

Loading...

Loading...