Debug

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 13-41

ID012310 Non-Confidential, Unrestricted Access

aborts, the processor latches the abort and its type until the processor leaves Debug state, in the

same way as if an imprecise data abort is detected in normal operation when the A bit in the

CPSR is set. The aborts are not taken immediately.

When the processor sets this bit, any memory accesses from Debug state that cause imprecise

data aborts cause DSCR[7], sticky imprecise data abort, to be set, but are otherwise discarded.

The cause and type of the abort are not recorded. In particular, if an abort is still latched from

the initial Data Memory Barrier that was completed on entry to Debug state, it is not overwritten

by the new abort. Following writes to memory by the debugger it issues a Data Memory Barrier

operation to ensure imprecise data aborts are detected.

Before exit from Debug state, a debugger must issue a Data Memory Barrier operation. On exit

from Debug state, DSCR[19] is cleared by the processor.

If an imprecise data abort has occurred during the period between entry to Debug state and the

when the processor set DSCR[19], it is taken by the processor on exit from Debug state,

providing the A bit in the CPSR is not set. If the A bit in the CPSR is set, it is pended until the

A bit in the CPSR is cleared, as for normal operation.

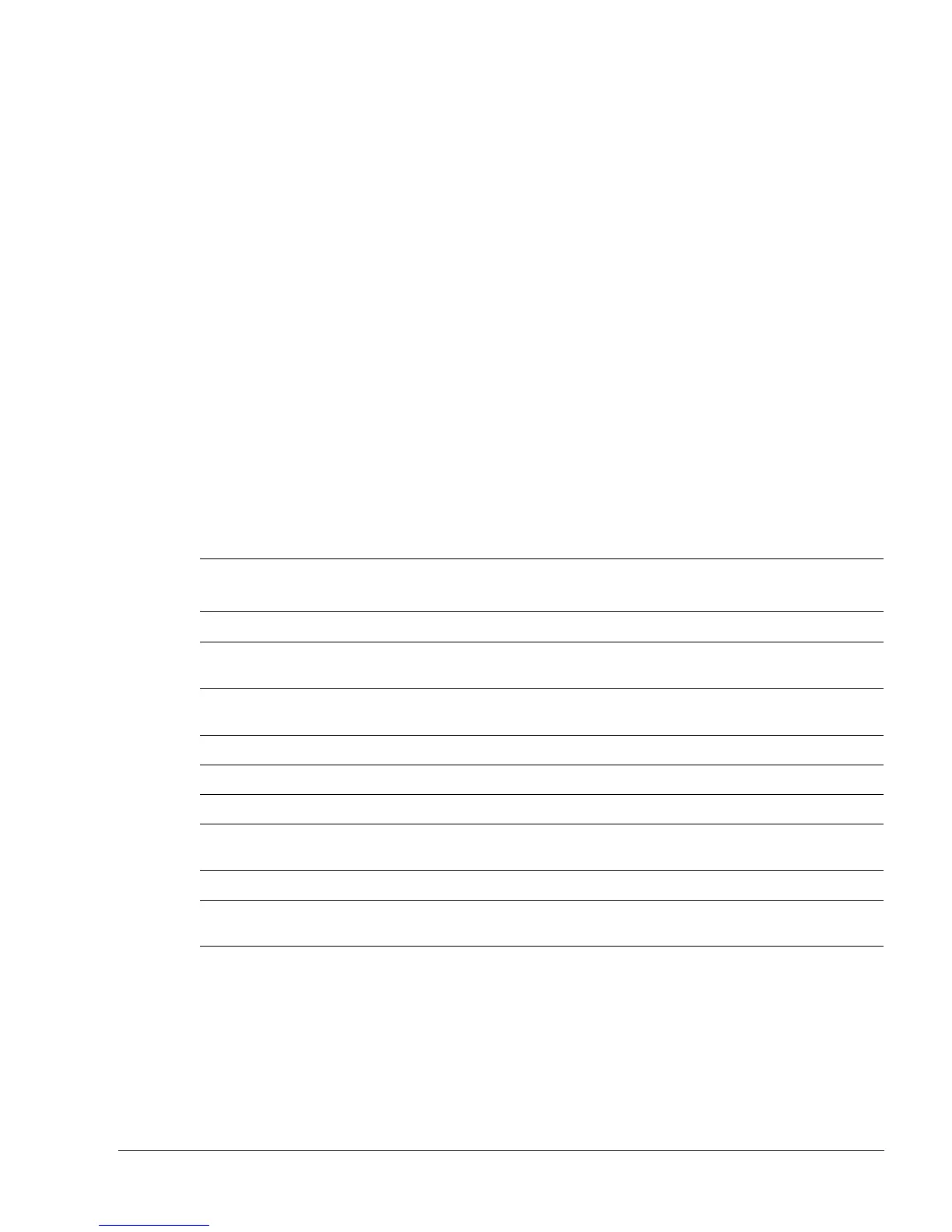

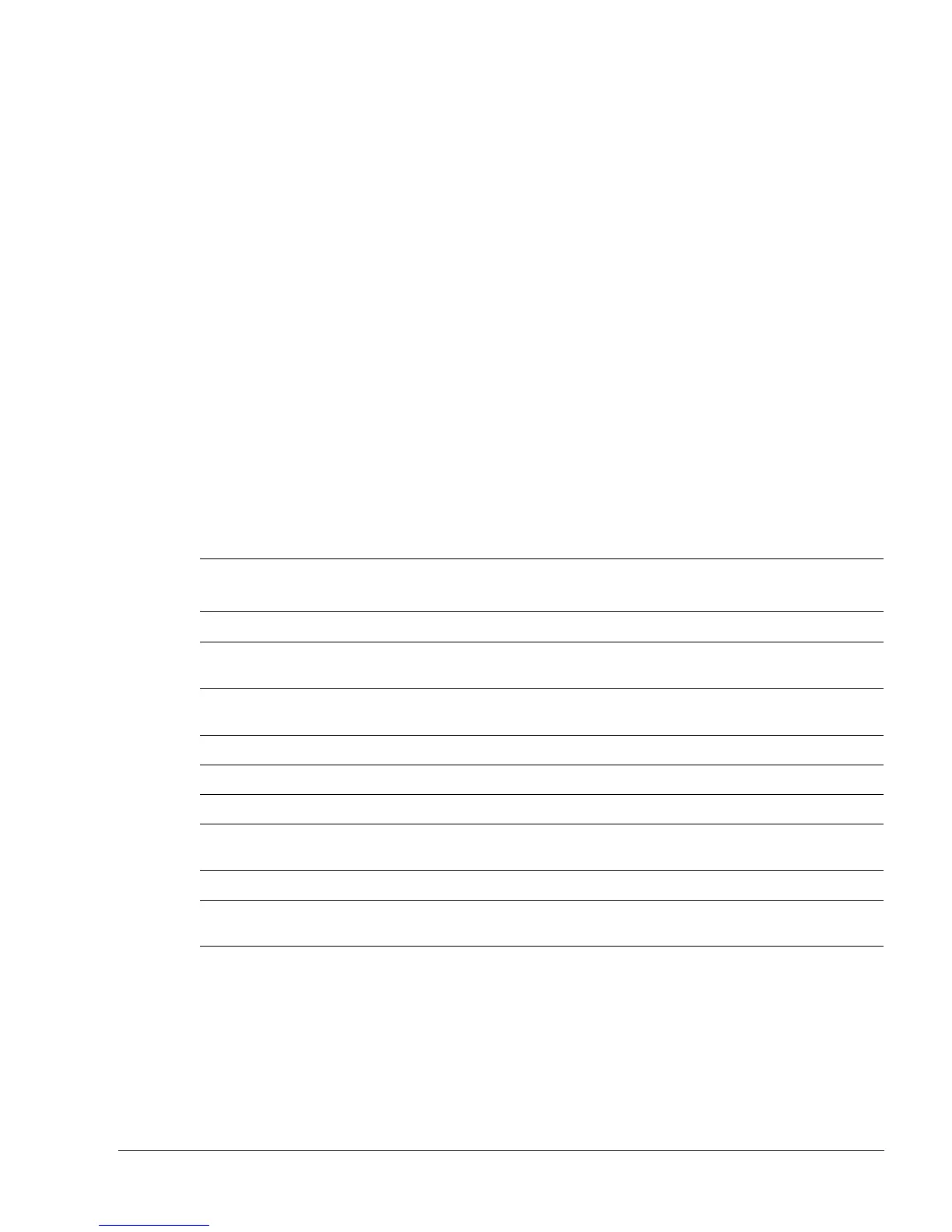

Table 13-26 lists an example sequence of a memory operation executed in normal operation that

eventually causes an imprecise abort when the processor is in Debug state. In addition, a

memory operation issued by the debugger in Debug state causes a second imprecise abort that

is ignored by the processor, apart from the sticky imprecise data abort bit being set. Throughout

the example the A bit in the CPSR is clear.

Table 13-26 Example memory operation sequence

Operation Result

Debug

state?

DCSR[19] DCSR[7]

Abort

latched?

Abort

taken?

1 Memory write Buffered operation No 0 0

2 Debug

exception

Enters Debug state Yes 0 0

3Data Memory

Barrier

Buffered operation flushed

- imprecise data abort

Yes 0

1

a

Yes

No

b

4 Processor sets DSCR[19] Yes 1 1

5 DSCR read Clears sticky bits Yes 1 0

6 Memory write Buffered operation Yes 1 0

7Data Memory

Barrier

Buffered operation flushed

- imprecise data abort

Yes 1 1

No

c

No

8 DSCR read Clears sticky bits Yes 1 0

9 Exit Debug

state

Processor clears DSCR[19] No 0 0

Yes

d

(d)

a. The sticky imprecise data abort bit is set because an imprecise data abort was signalled in Debug state.

b. Abort is not taken because the processor is in Debug state.

c. Abort is not latched because DSCR[19] is set.

d. The previous abort latched on row (3) is taken, now the processor has left Debug state and the A bit in the CPSR is not set.

Loading...

Loading...