Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 2-34

ID012310 Non-Confidential, Unrestricted Access

ClearExclusiveLocal(processor_id)

2.11.4 CLREX

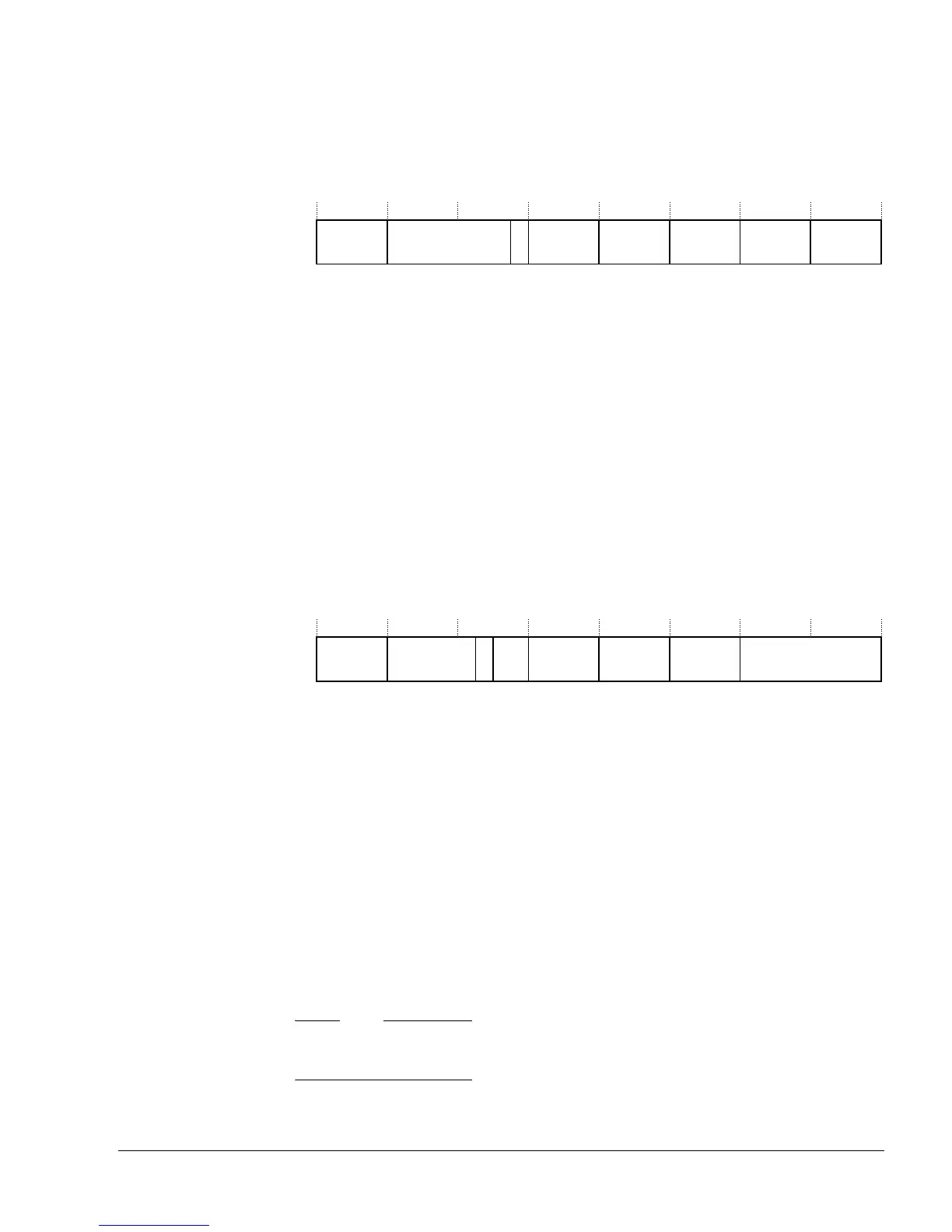

Figure 2-17 shows the format of the Clear Exclusive, CLREX, instruction.

Figure 2-17 CLREX instruction

The dummy STREX construct specified in ARMv6 is required for correct system behavior. The

CLREX instruction replaces the dummy STREX instruction.

This operation in unconditional in the ARM instruction set.

Syntax

CLREX

Operation

ClearExclusiveLocal(processor_id)

2.11.5 NOP-compatible hints

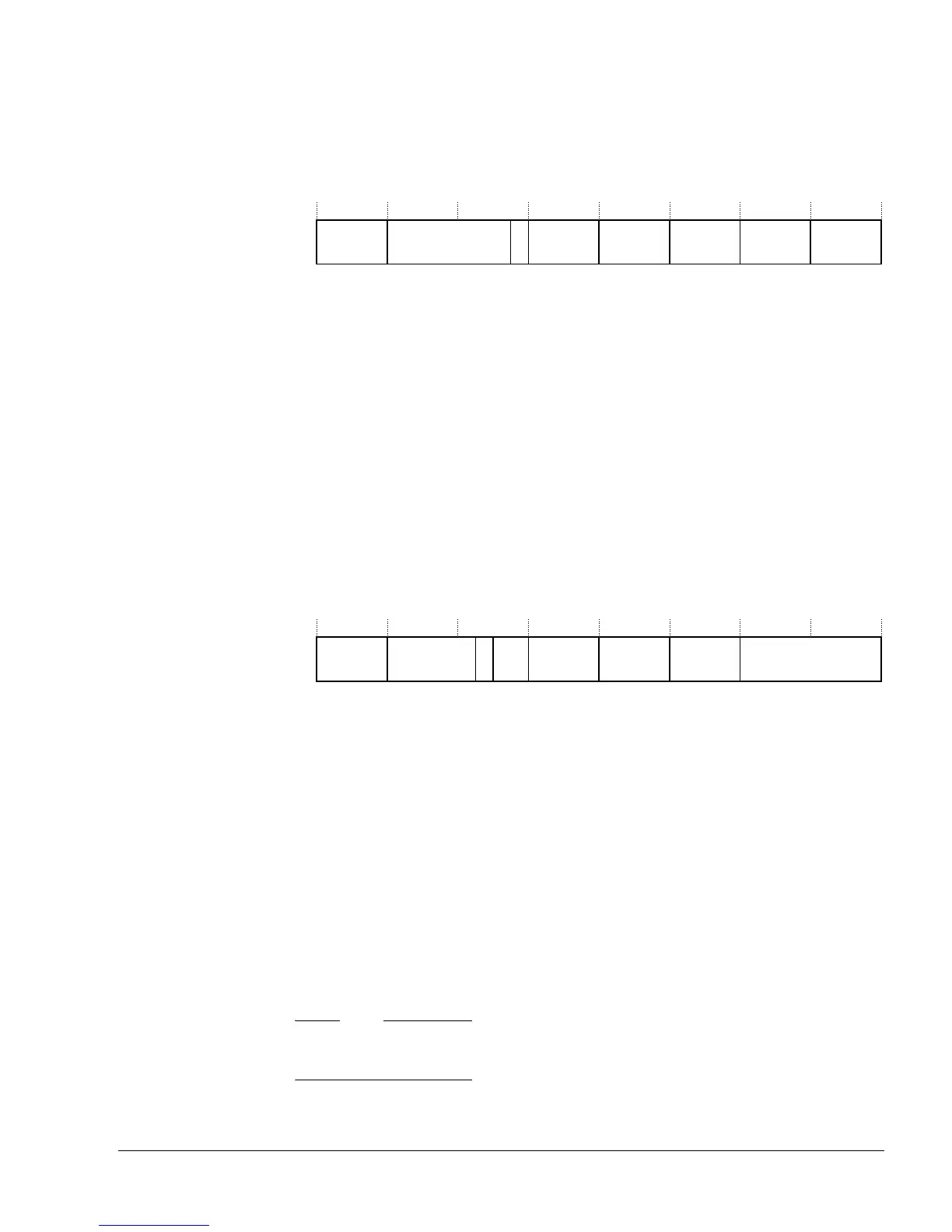

Figure 2-18 shows the format of the NOP-compatible hint instruction.

Figure 2-18 NOP-compatible hint instruction

Syntax

<cond>

Is the condition when the instruction executes. It produces no useful change in

functionality, but is provided to ensure disassembly followed by reassembly

always regenerates the original code.

<hint>

defaults to zero

hint == 0x0: the instruction is NOP

hint == 0x1: the instruction is YIELD

For all other values, RESERVED, the instruction behaves like NOP.

The true NOP for ARM state is equivalent to an MSR to the CPSR with the

immed_value

redefined as the hint field and no bytes selected. The instruction is fully architecturally defined,

with all encodings assigned.

Note

True NOPs are architected for alignment reasons and do not have any timing guarantees with

respect to their neighboring instructions.

01010 11111

31 28 27 21 20 19 16 15 12 11 8 7 4 3 0

1 1 SBO SBO SBZ 0 0 0 1 SBO

HintCond

31 28 27 23 22 21 20 19 16 15 12 11 8 7 0

0 0 1 1 0 0 1 0 0 0 0 0 SBO 0 0 0 0

Loading...

Loading...