Memory Management Unit

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 6-34

ID012310 Non-Confidential, Unrestricted Access

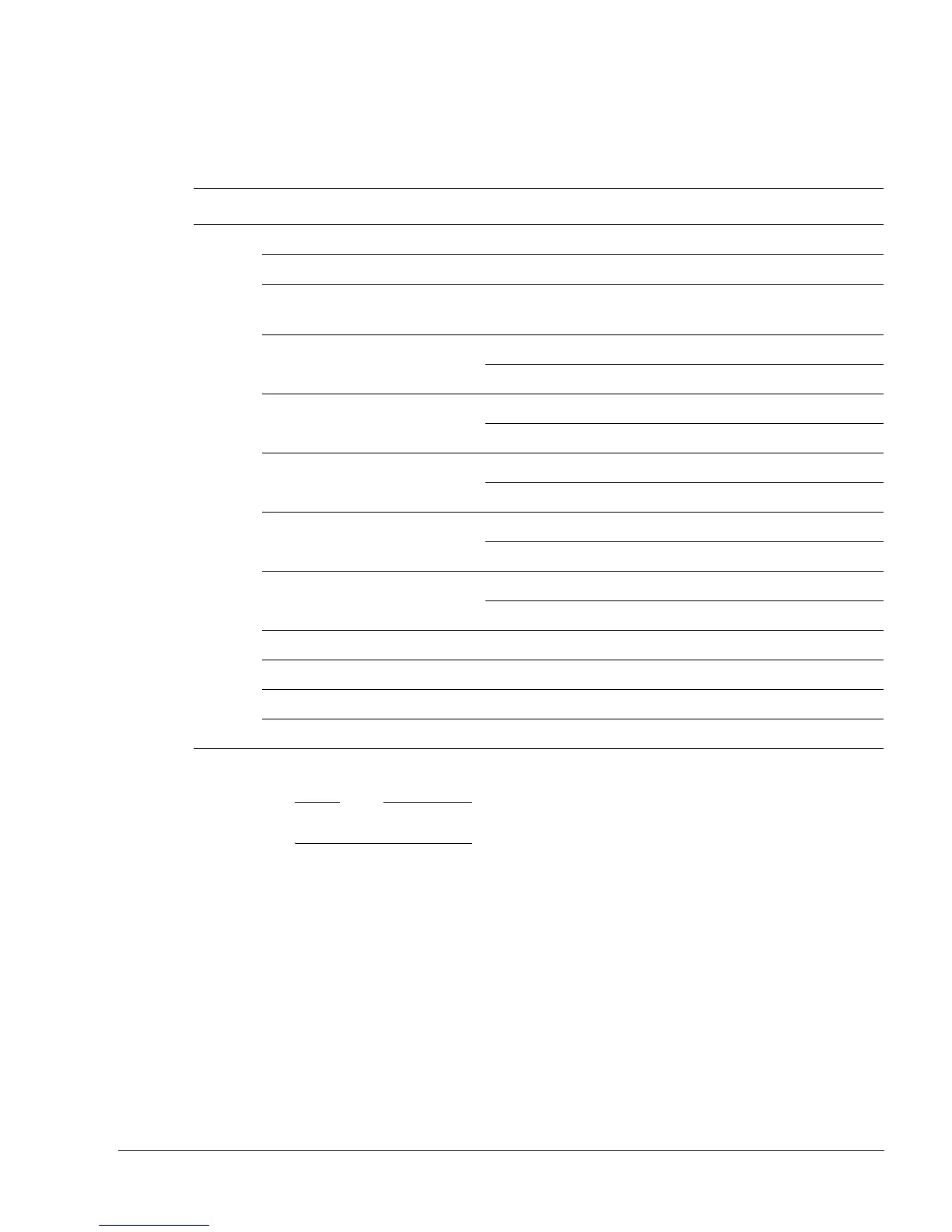

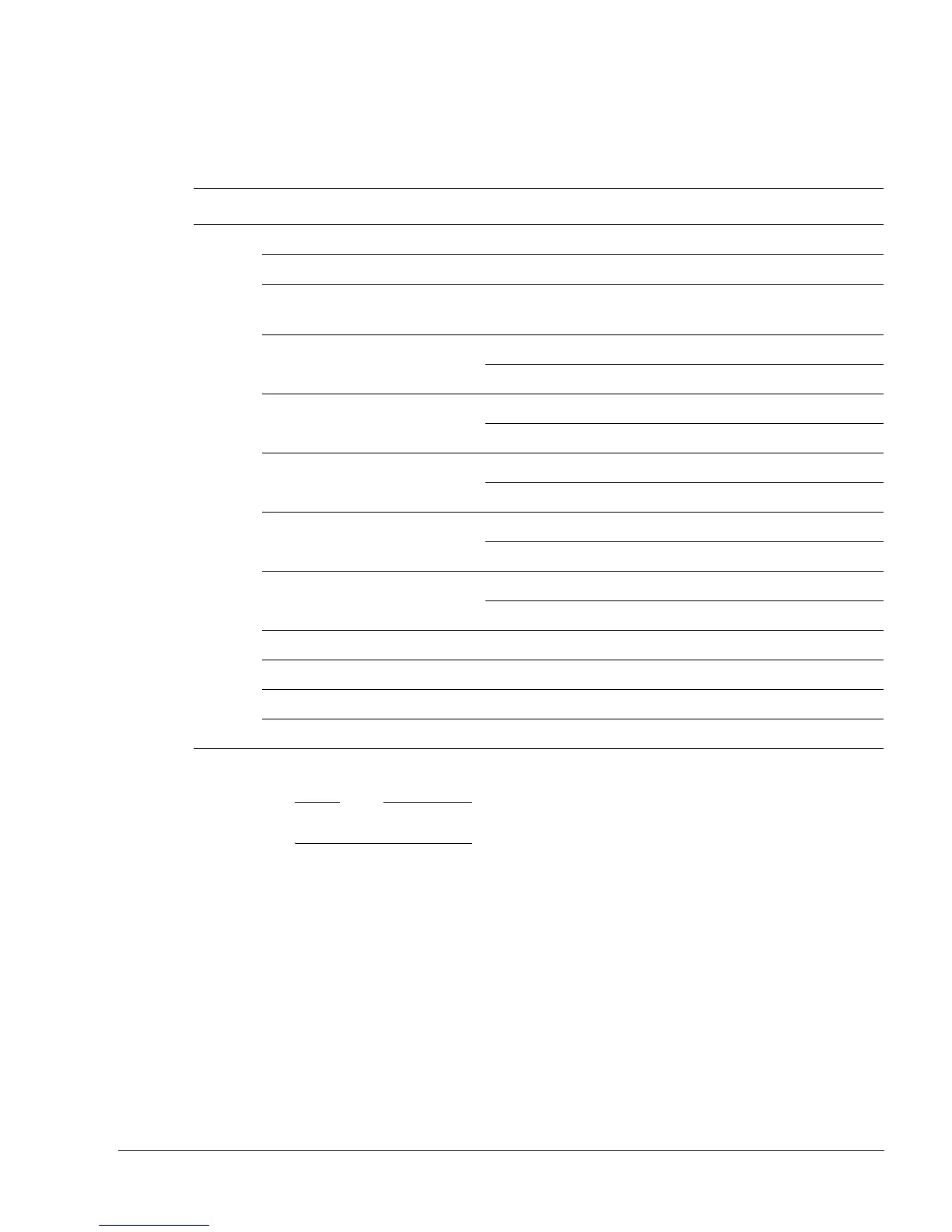

6.10 Fault status and address

Table 6-11 lists the encodings for the Fault Status Register.

Note

All other Fault Status encodings are reserved.

If a translation abort occurs during a Data Cache maintenance operation by virtual address, then

a Data Abort is taken and the DFSR indicates the reason. The FAR indicates the faulting address,

and the IFAR indicates the address of the instruction causing the abort.

If a translation abort occurs during an Instruction Cache maintenance operation by virtual

address, then a Data Abort is taken, and an Instruction Cache Maintenance Operation Fault is

indicated in the DFSR. The IFSR indicates the reason. The FAR indicates the faulting address,

and the IFAR indicates the address of the instruction causing the abort.

Domain and fault address information is only available for data accesses. For instruction aborts

R14 must be used to determine the faulting address. You can determine the domain information

by performing a TLB lookup for the faulting address and extracting the domain field.

Table 6-12 on page 6-35 lists a summary of the abort vector that is taken, and the Fault Status

and Fault Address Registers that are updated for each abort type.

Table 6-11 Fault Status Register encoding

Priority Sources FSR[10,3:0] Domain FSR[12]

Highest Alignment b00001 Invalid SBZ

TLB miss b00000 Invalid SBZ

Instruction cache maintenance

a

operation fault

b00100 Invalid SBZ

External abort on translation first-level b01100 Invalid SLVERR !DECERR

second-level b01110 Valid SLVERR !DECERR

Translation Section b00101 Invalid SBZ

Page b00111 Valid SBZ

Access Bit Fault, Force AP only Section b00011 Valid SBZ

Page b00110 Valid SBZ

Domain Section b01001 Valid SBZ

Page b01011 Valid SBZ

Permission Section b01101 Valid SBZ

Page b01111 Valid SBZ

Precise external abort b01000 Valid SLVERR !DECERR

Imprecise external abort b10110 Invalid SLVERR !DECERR

Parity error exception, not supported b11000 Invalid SBZ

Lowest Instruction debug event b00010 Valid SBZ

a. These aborts cannot be signaled with the IFSR because they do not occur on the instruction side.

Loading...

Loading...