Level Two Interface

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 8-27

ID012310 Non-Confidential, Unrestricted Access

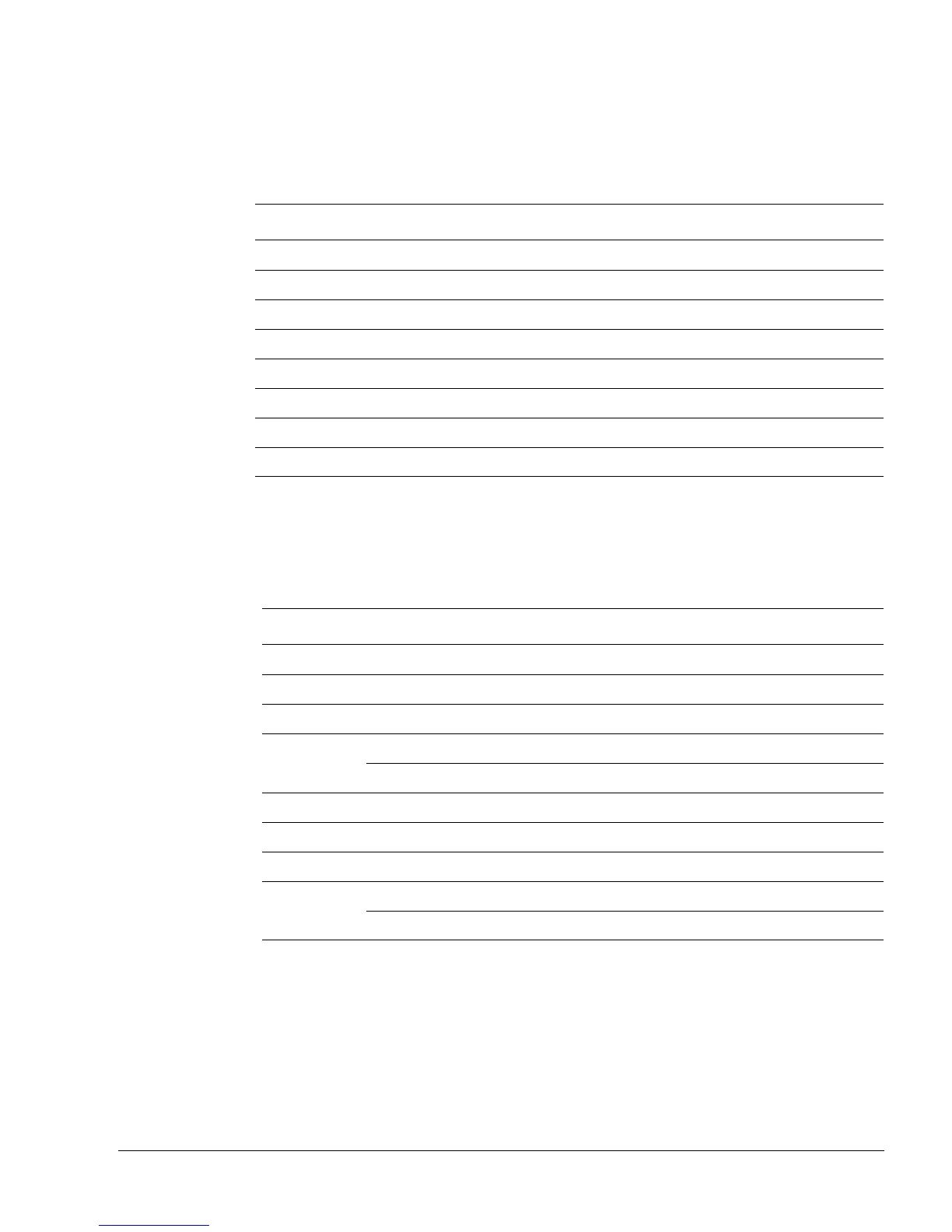

8.5.22 Cacheable Write-Through or Noncacheable STRB

Table 8-45 shows the values of AWADDRRW, AWBURSTRW, AWSIZERW, and

AWLENRW for STRBs over the Data Read/Write Interface.

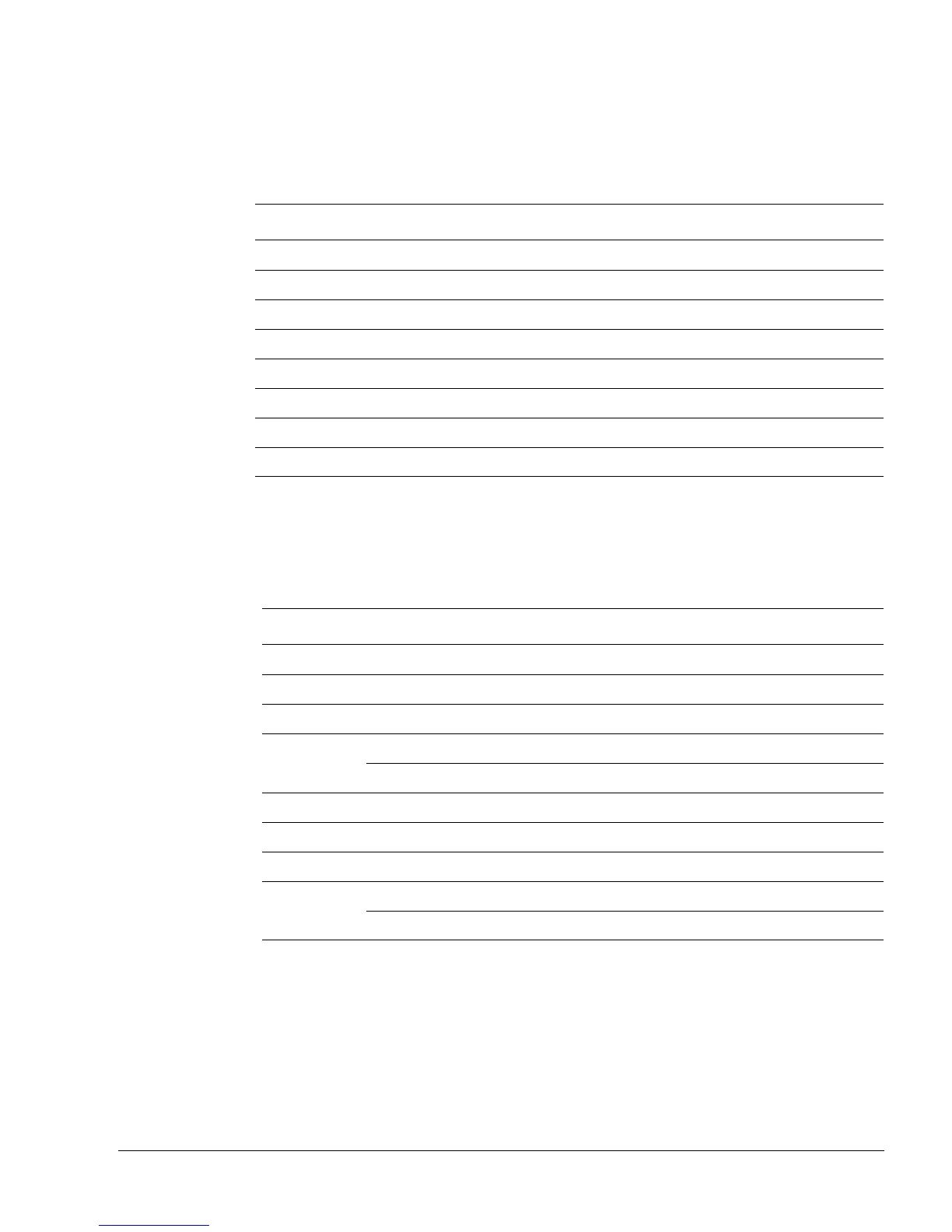

8.5.23 Cacheable Write-Through or Noncacheable STRH

Table 8-46 shows the values of AWADDRRW, AWBURSTRW, AWSIZERW, and

AWLENRW for STRHs over the Data Read/Write Interface.

Table 8-45 Cacheable Write-Through or Noncacheable STRB

Address[4:0] AWADDRRW AWBURSTRW AWSIZERW AWLENRW WSTRBRW

0x00

, byte 0

0x00

Incr 8-bit 1 data transfer b0000 0001

0x01

, byte 1

0x01

Incr 8-bit 1 data transfer b0000 0010

0x02

, byte 2

0x02

Incr 8-bit 1 data transfer b0000 0100

0x03

, byte 3

0x03

Incr 8-bit 1 data transfer b0000 1000

0x04

, byte 4

0x04

Incr 8-bit 1 data transfer b0001 0000

0x05

, byte 5

0x05

Incr 8-bit 1 data transfer b0010 0000

0x06

, byte 6

0x06

Incr 8-bit 1 data transfer b0100 0000

0x07

, byte 7

0x07

Incr 8-bit 1 data transfer b1000 0000

Table 8-46 Cacheable Write-Through or Noncacheable STRH

Address[4:0] AWADDRRW AWBURSTRW AWSIZERW AWLENRW WSTRBRW

0x00

, byte 0

0x00

Incr 16-bit 1 data transfer b0000 0011

0x01

, byte 1

0x01

Incr 32-bit 1 data transfer b0000 0110

0x02

, byte 2

0x02

Incr 16-bit 1 data transfer b0000 1100

0x03

, byte 3

0x03

Incr 8-bit 1 data transfer b0000 1000

0x04

Incr 8-bit 1 data transfer b0001 0000

0x04

, byte 4

0x04

Incr 16-bit 1 data transfer b0011 0000

0x05

, byte 5

0x05

Incr 32-bit 1 data transfer b0110 0000

0x06

, byte 6

0x06

Incr 16-bit 1 data transfer b1100 0000

0x07

, byte 7

0x07

Incr 8-bit 1 data transfer b1000 0000

0x08

Incr 8-bit 1 data transfer b0000 0001

Loading...

Loading...