Introduction

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 1-43

ID012310 Non-Confidential, Unrestricted Access

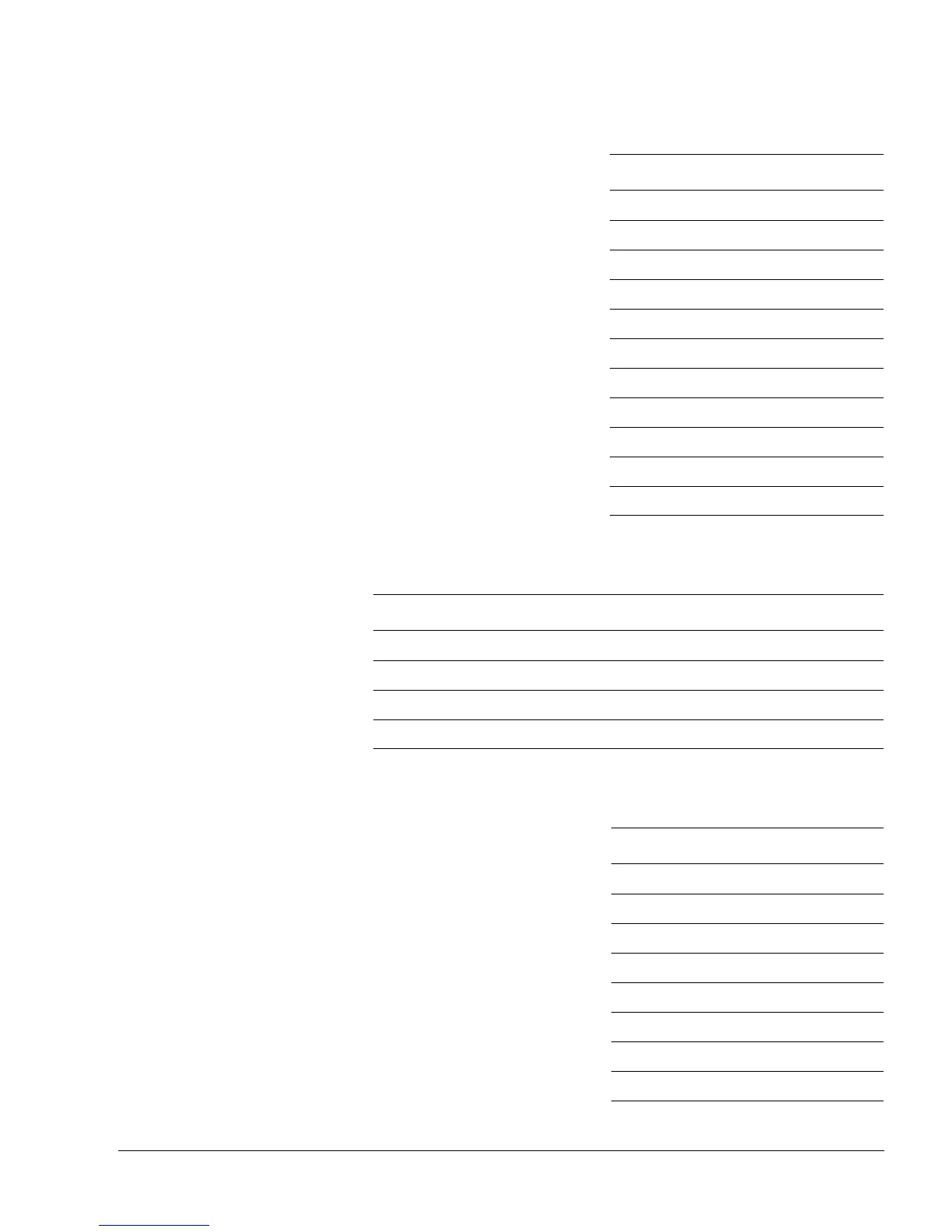

Table 1-13 summarizes Operand2 assembler.

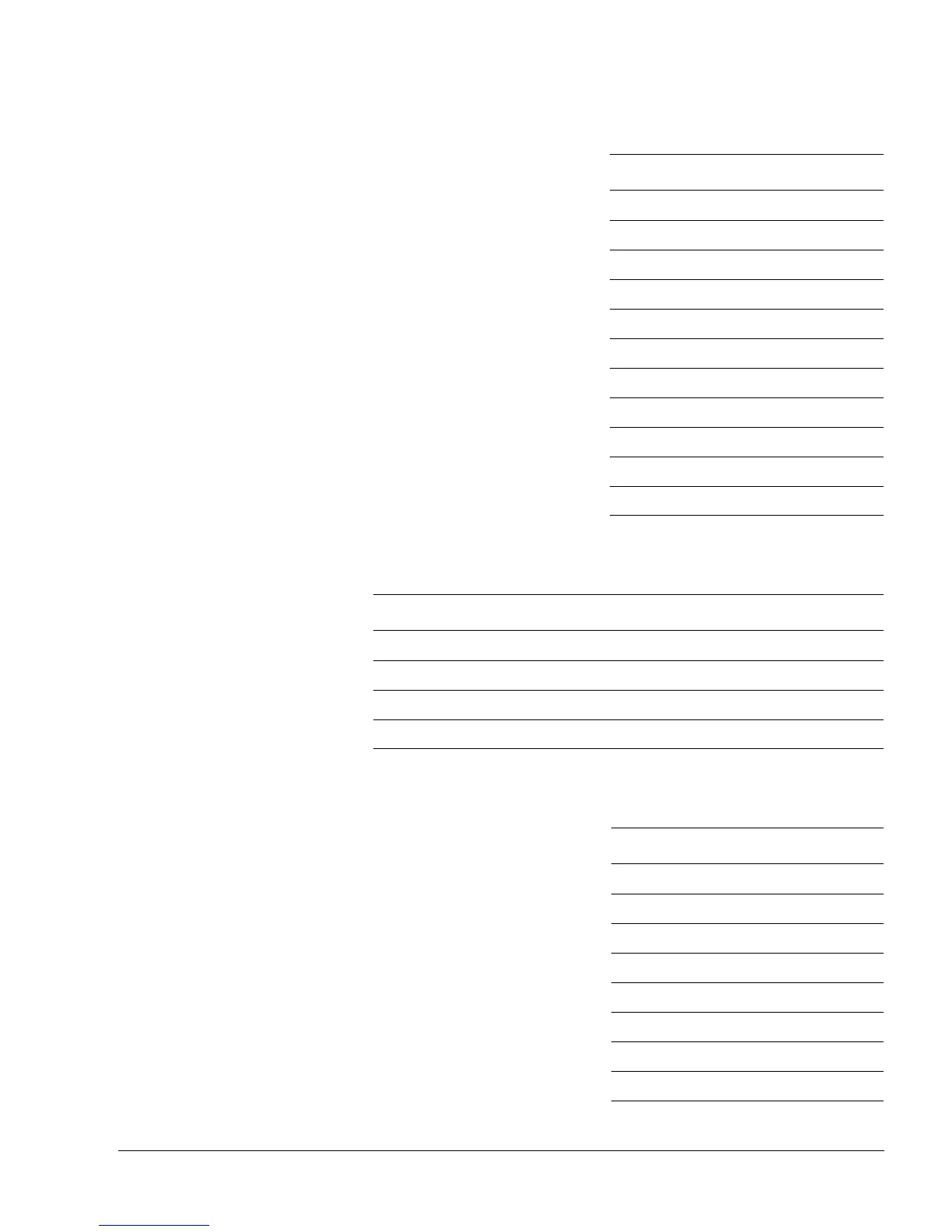

Table 1-14 summarizes the MSR instruction fields.

Table 1-15 summarizes condition codes.

Table 1-13 Operand2

Operation Assembler

Immediate value

#<immed_8r>

Logical shift left

<Rm> LSL #<immed_5>

Logical shift right

<Rm> LSR #<immed_5>

Arithmetic shift right

<Rm> ASR #<immed_5>

Rotate right

<Rm> ROR #<immed_5>

Register

<Rm>

Logical shift left

<Rm> LSL <Rs>

Logical shift right

<Rm> LSR <Rs>

Arithmetic shift right

<Rm> ASR <Rs>

Rotate right

<Rm> ROR <Rs>

Rotate right extended

<Rm> RRX

Table 1-14 Fields

Suffix Sets this bit in the MSR field_mask MSR instruction bit number

c

Control field mask bit, bit 0 16

x

Extension field mask bit, bit 1 17

s

Status field mask bit, bit 2 18

f

Flags field mask bit, bit 3 19

Table 1-15 Condition codes

Suffix Description

EQ

Equal

NE

Not equal

HS/CS

Unsigned higher or same, carry set

LO/CC

Unsigned lower, carry clear

MI

Negative, minus

PL

Positive or zero, plus

VS

Overflow

VC

No overflow

HI

Unsigned higher

Loading...

Loading...