Trace Interface Port

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 15-7

ID012310 Non-Confidential, Unrestricted Access

Table 15-9 lists the coprocessor interface signals.

A complete transaction takes three cycles. The first and last cycles can overlap, giving a

sustained rate of one every two cycles.

Note

Because current ETMs do not use the ETMCPRDATA[31:0] signal you must ensure that the

signal is tied off to

0x00000000

.

Only the following instructions are presented by the coprocessor interface:

MRC p14, 1, <Rd>, c0, <CRm>, <Op2>

MCR p14, 1, <Rd>, c0, <CRm>, <Op2>

MCR p15, 0, <Rd>, c13, c0, 1

The ETMCPSECCTL[1:0] signals indicate when the access to the coprocessor registers is

Non-secure and when the trace is prohibited. Table 15-10 lists the format of the

ETMCPSECCTL[1:0] signals.

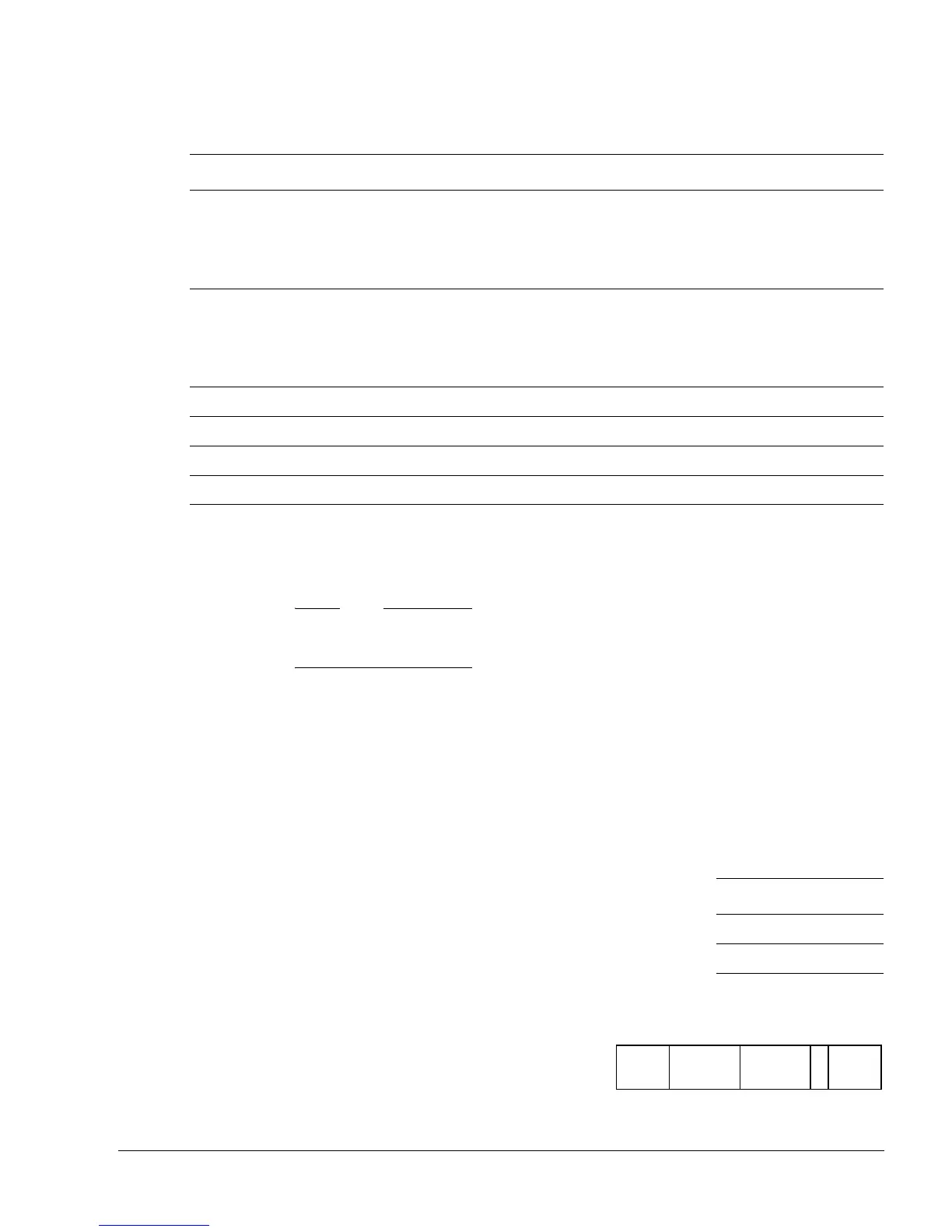

Figure 15-1 shows the format of the ETMCPADDRESS[14:0] signals.

Figure 15-1 ETMCPADDRESS format

Table 15-9 Coprocessor interface signals

Signal name Direction Description Qualified by Reg bound

ETMCPENABLE Output Interface enable.

ETMCPWRITE and

ETMCPADDRESS are valid this

cycle, and the remaining signals

are valid two cycles later.

None

No, late

a

ETMCPCOMMIT Output Commit. If this signal is LOW

two cycles after

ETMCPENABLE is asserted,

the transfer is canceled and must

not take any effect.

ETMCPENABLE +2

No, late

a

ETMCPWRITE Output Read or write. Asserted for write. ETMCPENABLE Ye s

ETMCPADDRESS[14:0] Output Register number. ETMCPENABLE Ye s

ETMCPRDATA[31:0] Input Read data. ETMCPCOMMIT Yes

ETMCPWDATA[31:0] Output Write value. ETMCPCOMMIT Ye s

a. Used as a clock enable for coprocessor interface logic.

Table 15-10 ETMCPSECCTL[1:0] format

Bit Description

[1] Trace prohibited

[0] Non-secure access

14 12 11 8 7 4 3 2 0

Opcode

1

CRn CRm

C

P

Opcode

2

Loading...

Loading...