System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-71

ID012310 Non-Confidential, Unrestricted Access

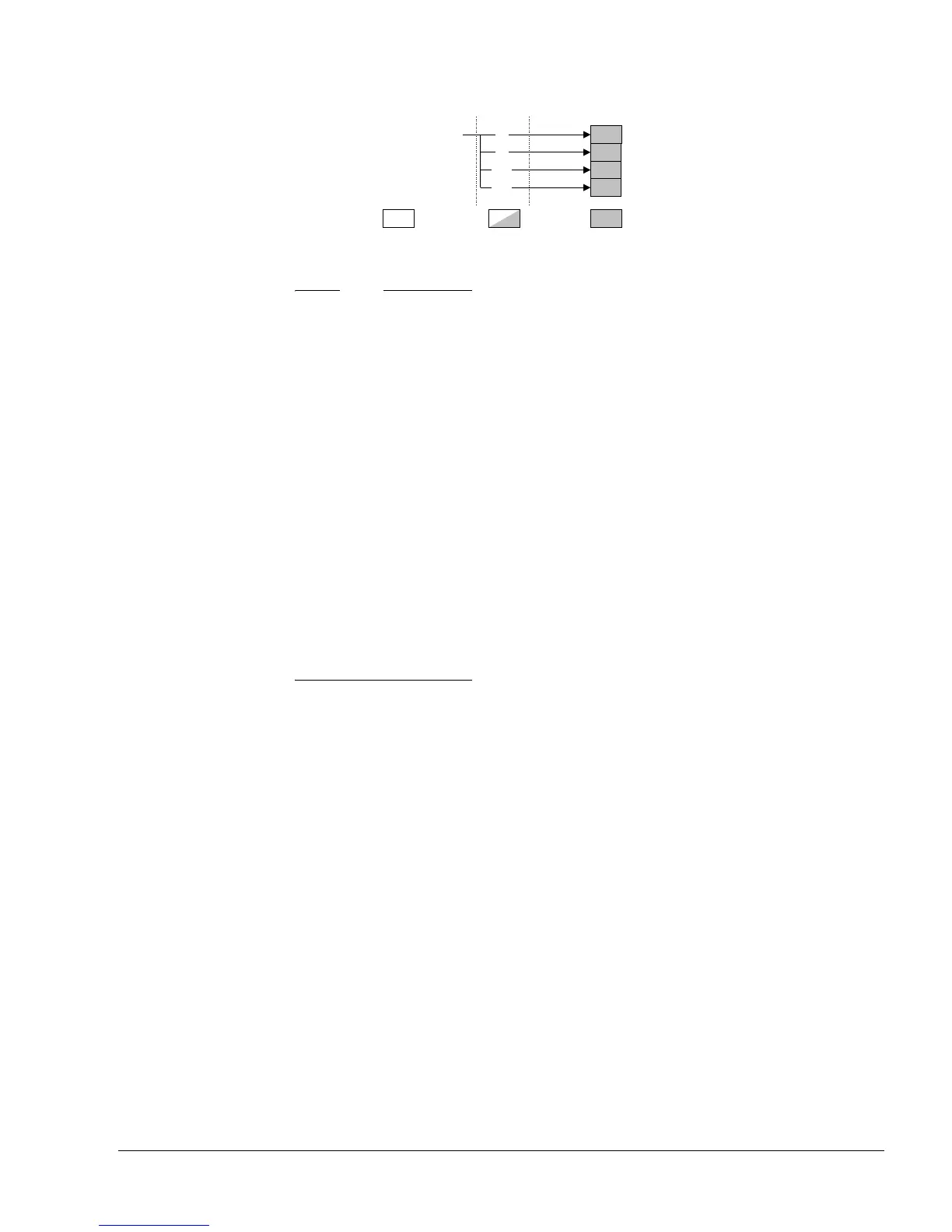

Figure 3-39 Cache operations with MCRR instructions

Note

• Writing c7 with a combination of CRm and Opcode_2 not listed in Figure 3-38 on

page 3-70 or CRm not listed in Figure 3-39 results in an Undefined exception apart from

the following operations, that are architecturally defined as unified cache operations and

have no effect:

—

MCR p15,0,<Rd>,c7,c7,{1-7}

—

MCR p15,0,<Rd>,c7,c11,{0-7}

—

MCR p15,0,<Rd>,c7,c15,{0-7}

.

• In the ARM1176JZF-S processor, reading from c7, except for reads from the Cache Dirty

Status Register or PA Register, causes an Undefined instruction trap.

• Writes to the Cache Dirty Status Register cause an Undefined exception.

• If Opcode_1 = 0, these instructions are applied to a level one cache system. All other

Opcode_1 values are reserved.

• All accesses to c7 can only be executed in a privileged mode of operation, except Data

Synchronization Barrier, Flush Prefetch Buffer, Data Memory Barrier, and Clean Data

Cache Range. These can be operated in User mode. Attempting to execute a privileged

instruction in User mode results in the Undefined instruction trap being taken.

There are three ways to use c7:

• For the Cache Dirty Status Register, read c7 with the MRC instruction.

• For range operations use the MCRR instruction with the value of CRm to select the

required operation.

• For all other operations use the MCR instruction to write to c7 with the combination of

CRm and Opcode_2 to select the required operation.

Depending on the operation you require set <Rd> for MCR instructions or <Rd> and

<Rn> for MCRR instructions to:

— Virtual Address (VA)

— Modified Virtual Address (MVA)

— Set and Index

— Should Be Zero.

Invalidate, Clean, and Prefetch operations

The purposes of the invalidate, clean, and prefetch operations that c7 provides are to:

• Invalidate part or all of the Data or Instruction caches

• Clean part or all of the Data cache

• Clean and Invalidate part or all of the Data cache

Read-only Read/write

VA

Using VA

c14

c5

c12

VA

0

Invalidate Instruction Cache Range

CRmOpcode_1

c6

VA

VA

VA

Invalidate Data Cache Range

Clean Data Cache Range

Clean and Invalidate Data Cache Range

Accessible in User mode

Loading...

Loading...