System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-87

ID012310 Non-Confidential, Unrestricted Access

Invalidate TLB unlocked entries

Invalidate TLB unlocked entries invalidates all the unlocked entries in the TLB. This function

causes a flush of the prefetch buffer. Therefore, all instructions that follow are fetched after the

TLB invalidation.

Invalidate TLB Entry by MVA

You can use Invalidate TLB Entry by MVA to invalidate all TLB entries for an area of memory

before you remap.

You must perform an Invalidate TLB Entry by MVA of an MVA in each area you want to remap,

section, small page, or large page.

This function invalidates a TLB entry that matches the provided MVA and ASID, or a global

TLB entry that matches the provided MVA.

This function invalidates a matching locked entry.

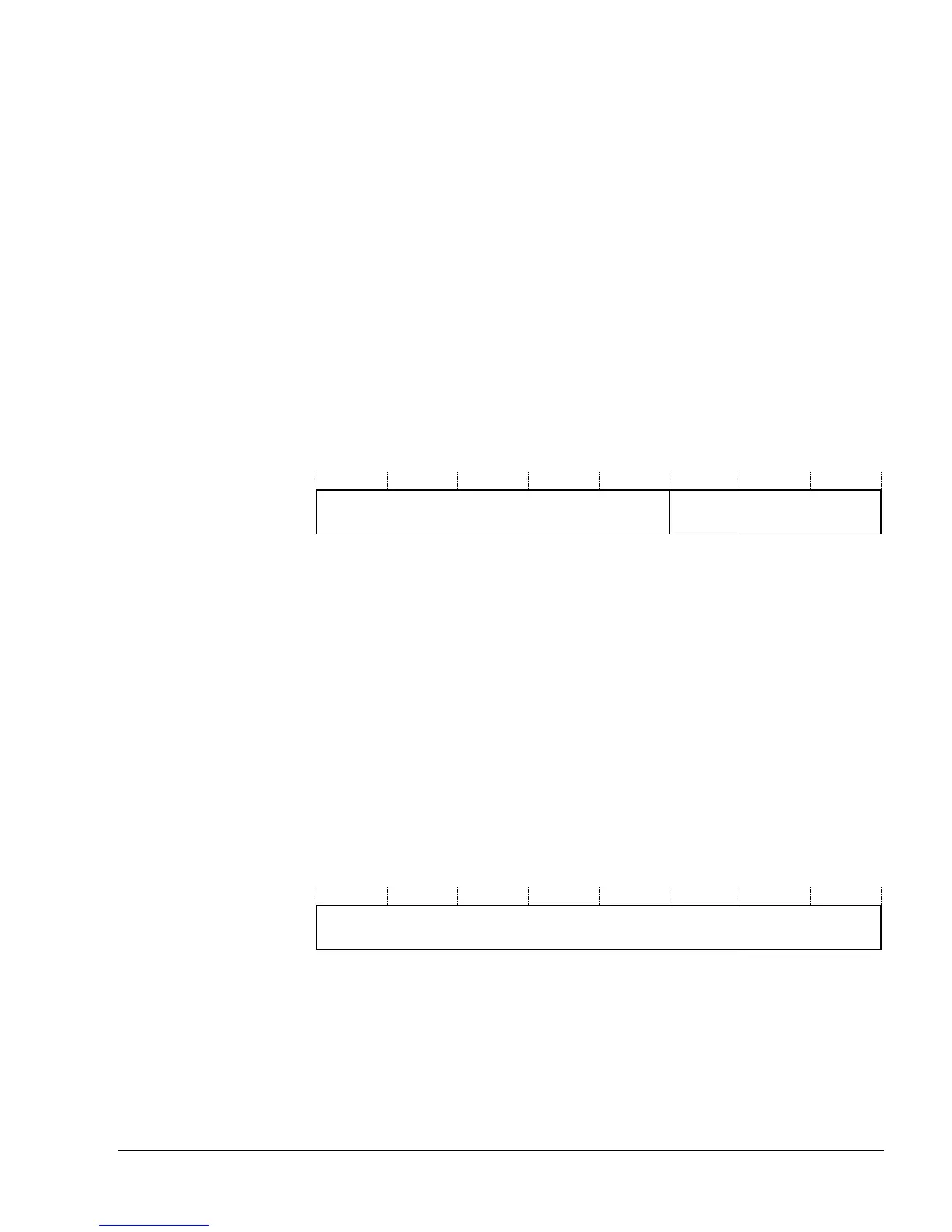

The Invalidate TLB Entry by MVA operation uses an MVA and ASID as an argument.

Figure 3-47 shows the format of this.

Figure 3-47 TLB Operations Register MVA and ASID format

Invalidate TLB Entry on ASID Match

This is a single interruptible operation that invalidates all TLB entries that match the provided

ASID value.

This function invalidates locked entries but does not invalidate entries marked as global.

In this processor this operation takes several cycles to complete and the instruction is

interruptible. When interrupted the R14 state is set to indicate that the MCR instruction has not

executed. Therefore, R14 points to the address of the MCR + 4. The interrupt routine then

automatically restarts at the MCR instruction. If the processor interrupts and later restarts this

operation, any entries fetched into the TLB by the interrupt that uses the provided ASID are

invalidated by the restarted invalidation.

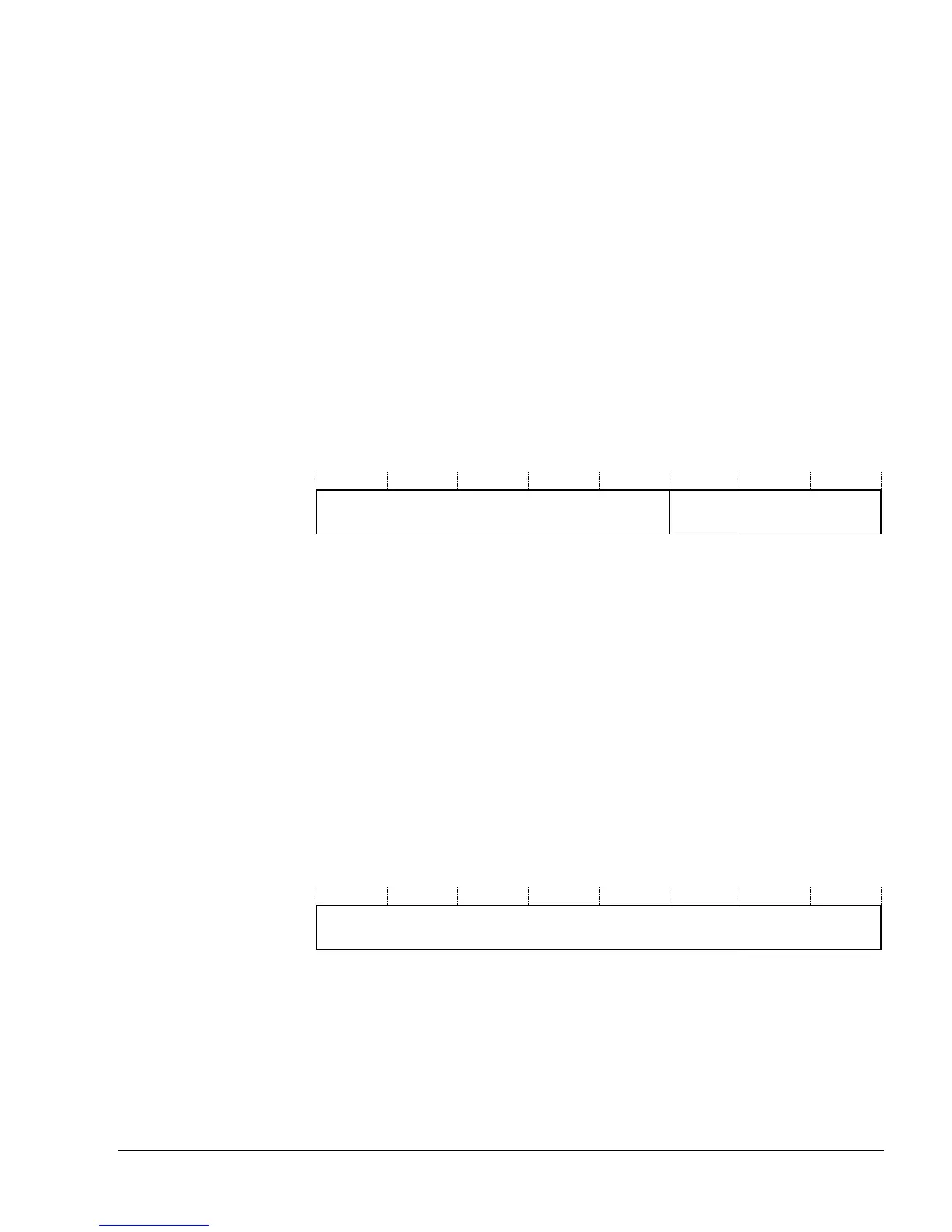

The Invalidate TLB Entry on ASID Match function requires an ASID as an argument.

Figure 3-48 shows the format of this.

Figure 3-48 TLB Operations Register ASID format

3.2.24 c9, Data and instruction cache lockdown registers

The purpose of the data and instruction cache lockdown registers is to provide a means to lock

down the caches and therefore provide some control over pollution that applications might

cause. With these registers you can lock down each cache way independently.

Modified virtual address

31 8 7 0

SBZ ASID

1112

31 8 7 0

SBZ ASID

Loading...

Loading...