System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-12

ID012310 Non-Confidential, Unrestricted Access

To use the system validation registers you read or write individual registers that make up the

group, see Use of the system control coprocessor.

You cannot use the System Validation Registers at the same time as the System Performance

Monitor Registers, because both sets of registers use the same physical counters. You must

disable one set of registers before starting to use the other set. See System performance monitor

on page 3-10.

System validation behaves in three ways:

• as a set of bits that enable specific system validation functionality

• as a set of operations that schedule and clear system validation events

• as a set of numbers, values that describe aspects of the caches and TCMs for system

validation.

3.1.10 Use of the system control coprocessor

This section describes the general method for use of the system control coprocessor.

You can access system control coprocessor CP15 registers with MRC and MCR instructions.

MCR{cond} P15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

MRC{cond} P15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

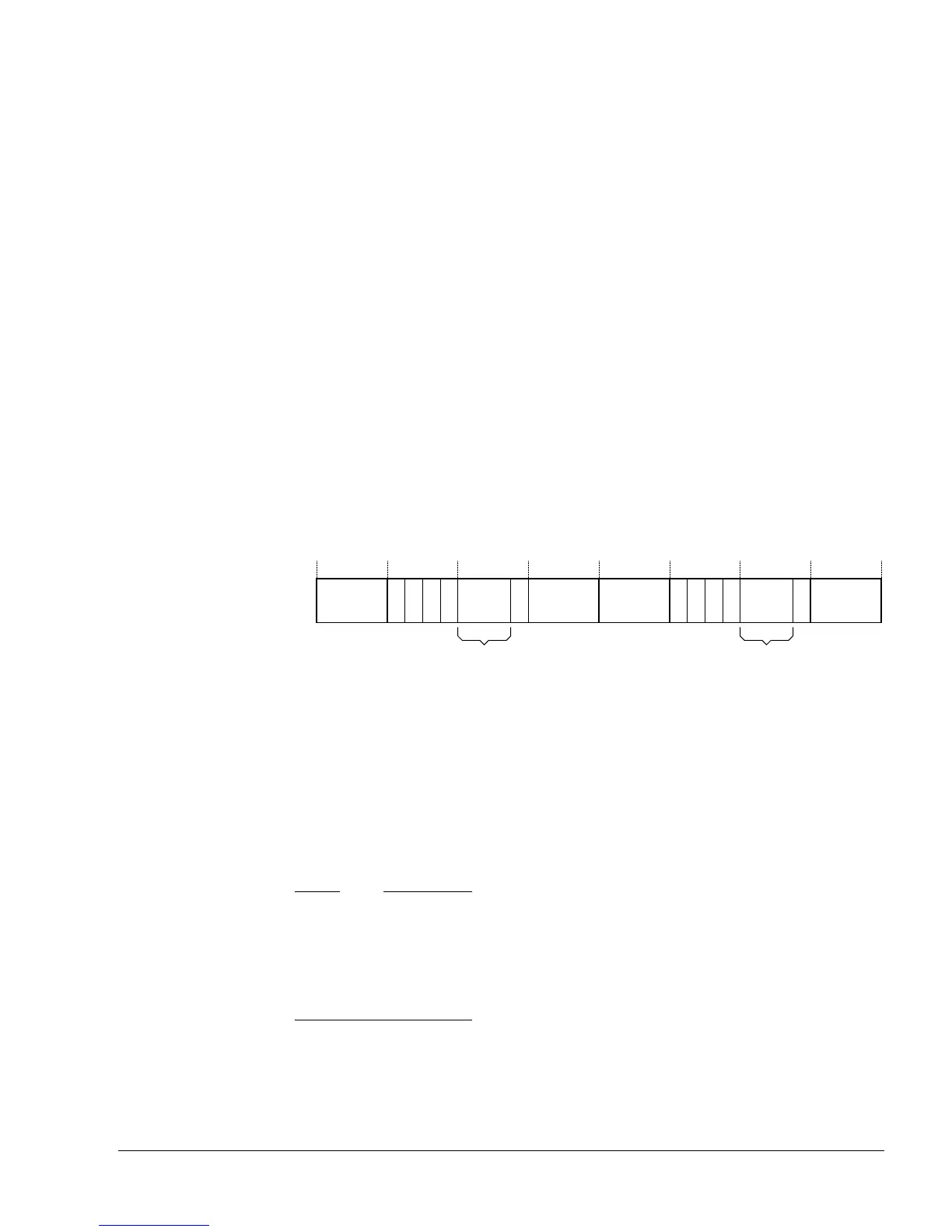

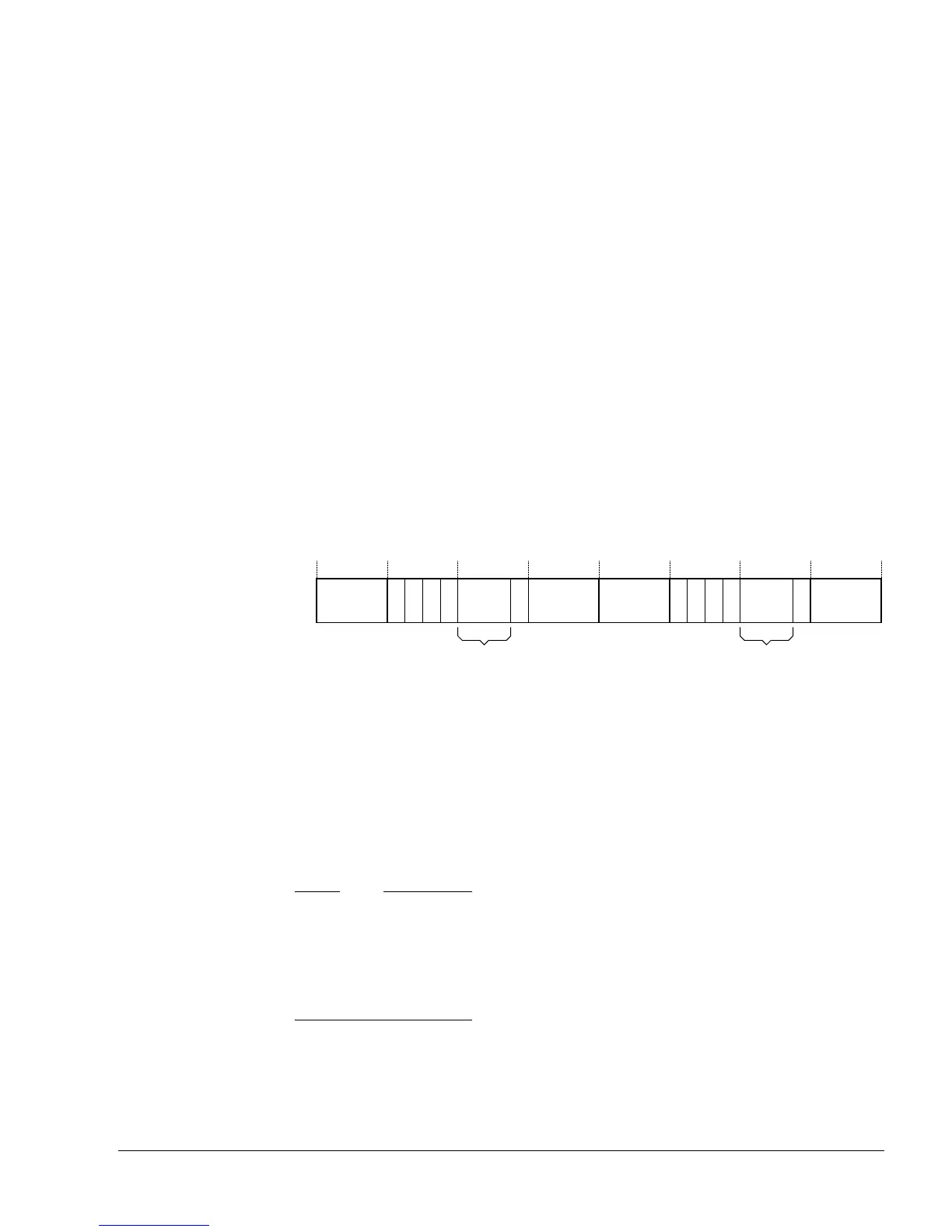

Figure 3-9 shows the instruction bit pattern of MRC and MCR instructions.

Figure 3-9 CP15 MRC and MCR bit pattern

The CRn field of MRC and MCR instructions specifies the coprocessor register to access. The

CRm field and Opcode_2 fields specify a particular operation when addressing registers. The L

bit distinguishes between an MRC (L=1) and an MCR (L=0).

Instructions CDP, LDC, and STC, together with unprivileged MRC and MCR instructions to

privileged-only CP15 registers, and Non-secure accesses to Secure registers, cause the

processor to take the Undefined instruction trap.

Note

Attempting to read from a nonreadable register, or to write to a nonwriteable register causes

Undefined exceptions.

The Opcode_1, Opcode_2, and CRm fields Should Be Zero in all instructions that access CP15,

except when the values specified are used to select required operations. Using other values

results in Undefined exceptions.

In all cases, reading from or writing any data values to any CP15 registers, including those fields

specified as Unpredictable (UNP), Should Be One (SBO), or Should Be Zero (SBZ), does not

cause any physical damage to the chip.

Cond

31 28 27 24 23

21

20 19 16 15 12 11 8 7 5 4 3 0

1 1 1 0

Opcode_1

L CRn Rd 1 1 1 1

Opcode_2

1 CRm

Loading...

Loading...