Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 2-33

ID012310 Non-Confidential, Unrestricted Access

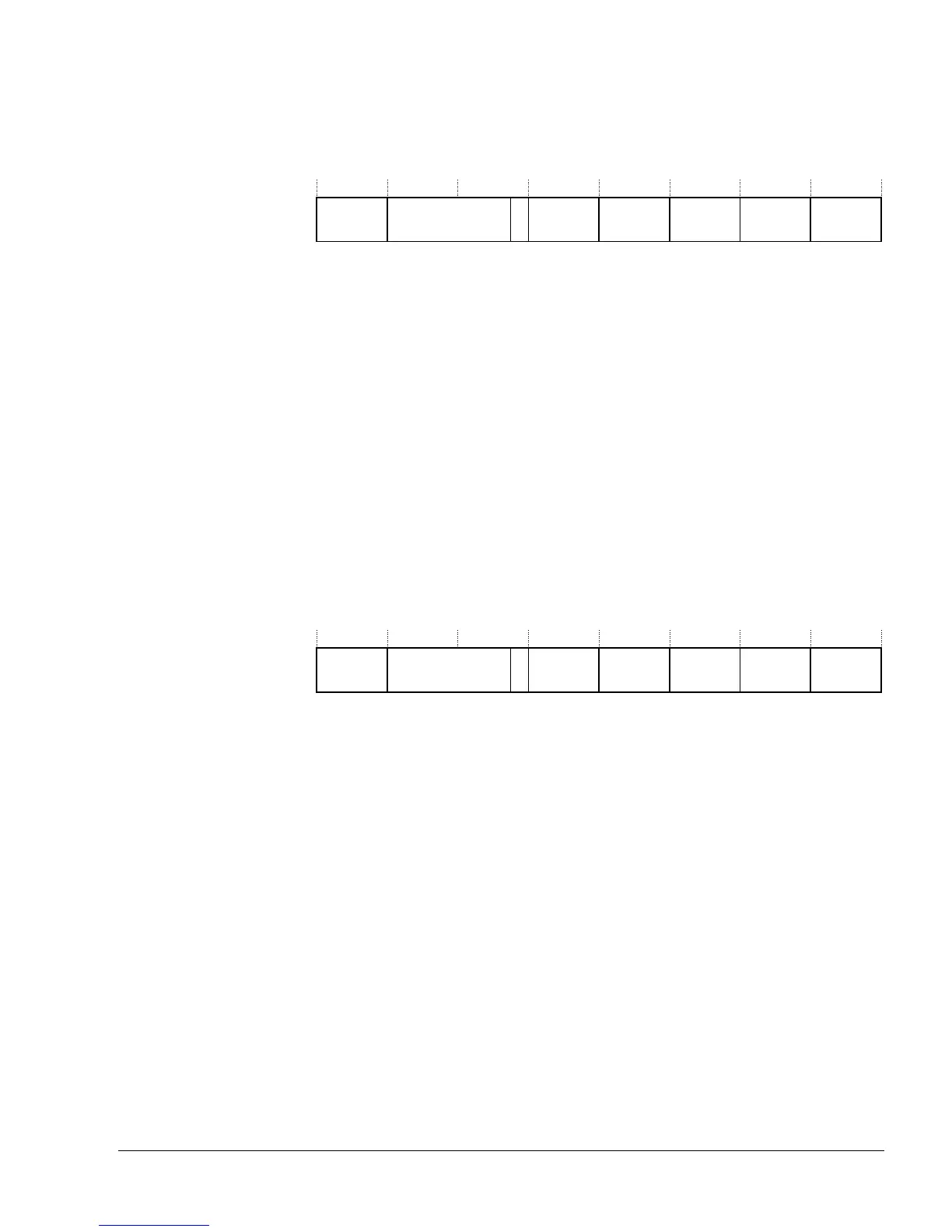

LDREXD

Figure 2-15 shows the format of the Load Register Doubleword Exclusive, LDREXD,

instruction.

Figure 2-15 LDREXD instruction

Syntax

LDREXD{<cond>} <Rd>, [<Rn>]

Operation

if ConditionPassed(cond) then

processor_id = ExecutingProcessor()

Rd = Memory[Rn,4]

R(d+1) = Memory[Rn+4,4]

if Shared(Rn) ==1 then

physical_address=TLB(Rn)

MarkExclusiveGlobal(physical_address,processor_id,8)

MarkExclusiveLocal(processor_id)

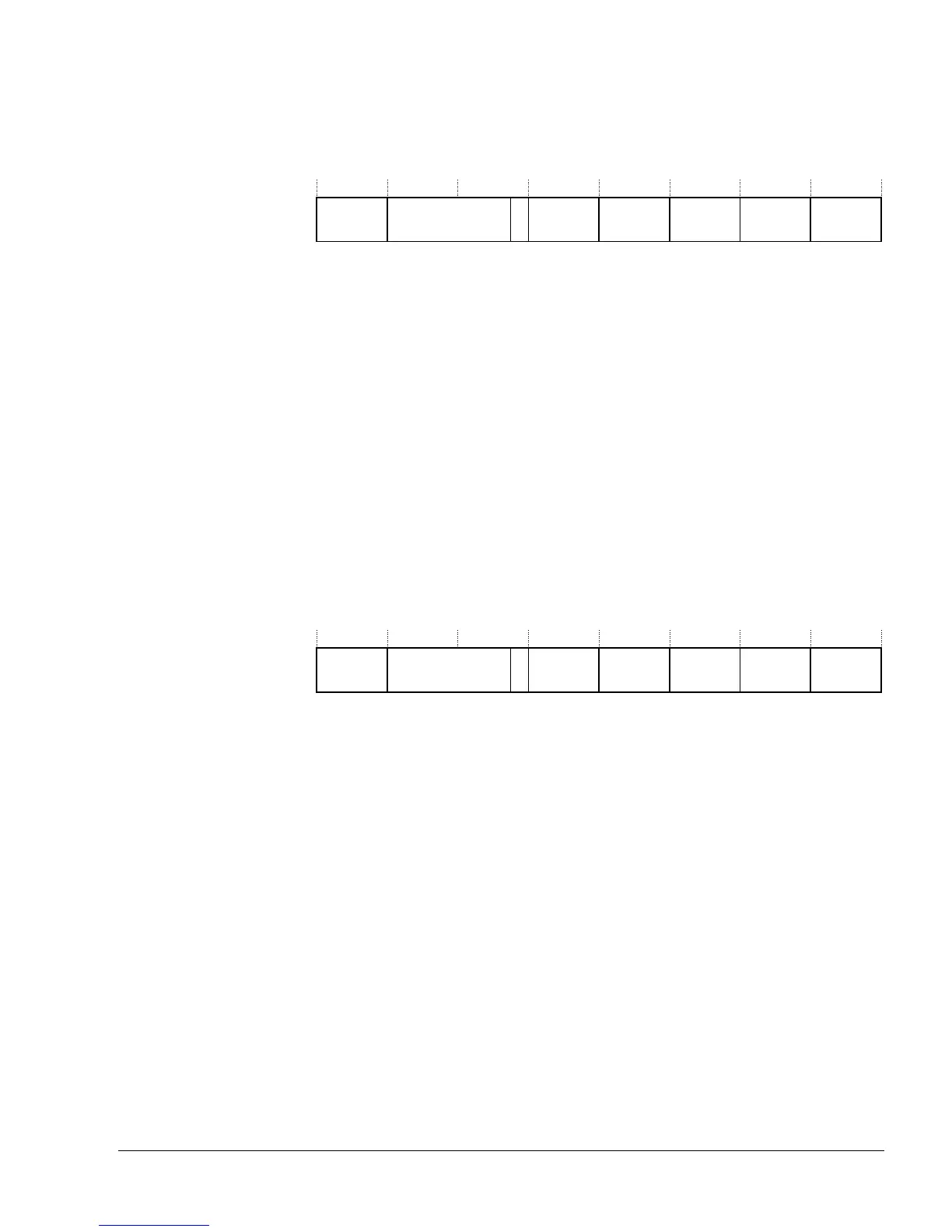

STREXD

Figure 2-16 shows the format of the Store Register Doubleword Exclusive, STREXD,

instruction.

Figure 2-16 STREXD instruction

Syntax

STREXD{<cond>} <Rd>, <Rm>, [<Rn>]

Operation

if ConditionPassed(cond) then

processor_id = ExecutingProcessor()

if IsExclusiveLocal(processor_id) then

if Shared(Rn)==1 then

physical_address=TLB(Rn)

if IsExclusiveGlobal(physical_address,processor_id,8) then

Memory[Rn,4] = Rm

Memory[Rn+4,4] = R(m+1)

Rd = 0

ClearByAddress(physical_address,8)

else

Rd =1

else

Memory[Rn,4] = Rm

Memory[Rn+4,4] = R(m+1)

Rd = 0

else

Rd = 1

SBOCond

31 28 27 21 20 19 15 12 11 7 4 3 0

0 0 0 1 1 0 1 1 Rn Rd SBO 1 0 0 1

16 8

RmCond

31 28 27 21 20 19 15 12 11 7 4 3 0

0 0 0 1 1 0 1 0 Rn Rd SBO 1 0 0 1

16 8

Loading...

Loading...