System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-44

ID012310 Non-Confidential, Unrestricted Access

3.2.7 c1, Control Register

This section contains information on:

• Purpose of the Control Register

• Structure of the Control Register

• Operation of the Control Register on page 3-45

• Use of the Control Register on page 3-47

• Behavior of the Control Register on page 3-48.

Purpose of the Control Register

The purpose of the Control Register is to provide control and configuration of:

• memory alignment, endianness, protection, and fault behavior

• MMU and cache enables and cache replacement strategy

• interrupts and the behavior of interrupt latency

• the location for exception vectors

• program flow prediction.

Table 3-39 on page 3-45 lists the purposes of the individual bits in the Control Register.

Structure of the Control Register

The Control Register is:

•in CP15 c1

• a 32 bit register, Table 3-39 on page 3-45 lists read and write access to individual bits for

the Secure and Non-secure worlds

• accessible in privileged modes only

• partially banked, Table 3-39 on page 3-45 lists banked and Secure modify only bits.

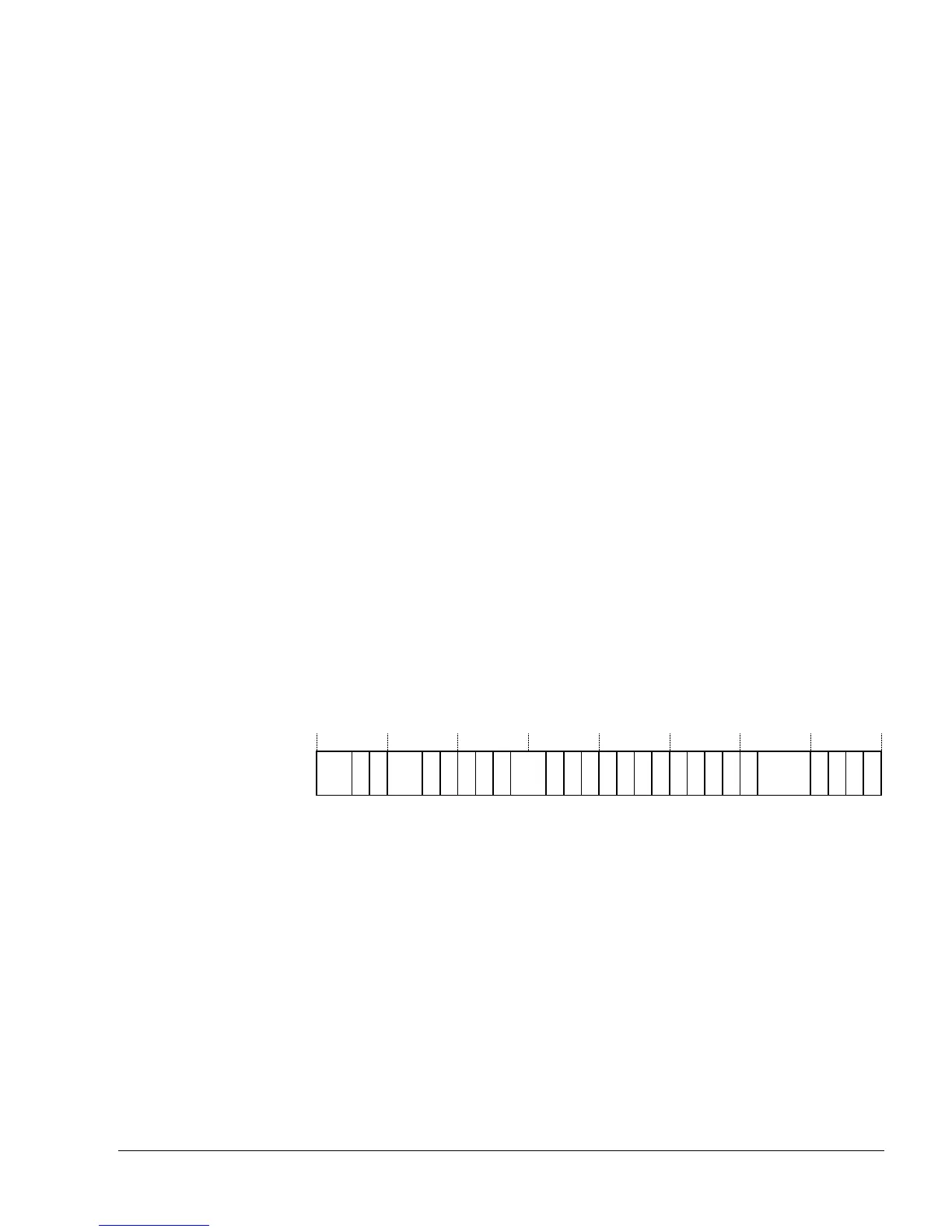

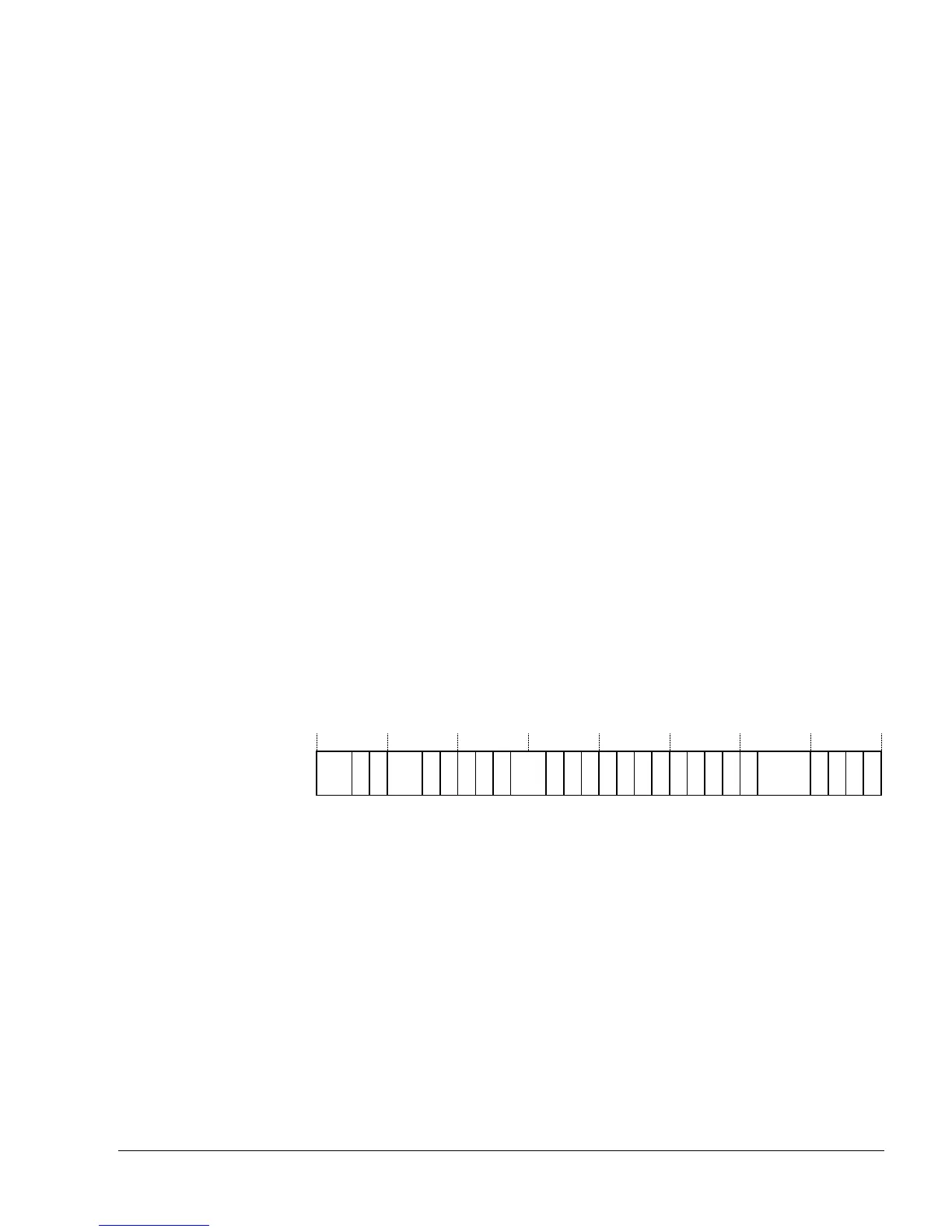

Figure 3-26 shows the arrangement of bits in the register.

Figure 3-26 Control Register format

F

A

T

R

SBZ MSBZ

31 25 24 23

22

21

20 19 18

17

16 15 14 13 12 11 10 9 8 7 6 4 3 2 1 0

V

E

X

P

U FI SBZ IT

S

B

Z

D

T

L4

R

R

V I Z F R S B SBO W C A

E

E

26272830 29

Loading...

Loading...