Unaligned and Mixed-endian Data Access Support

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 4-10

ID012310 Non-Confidential, Unrestricted Access

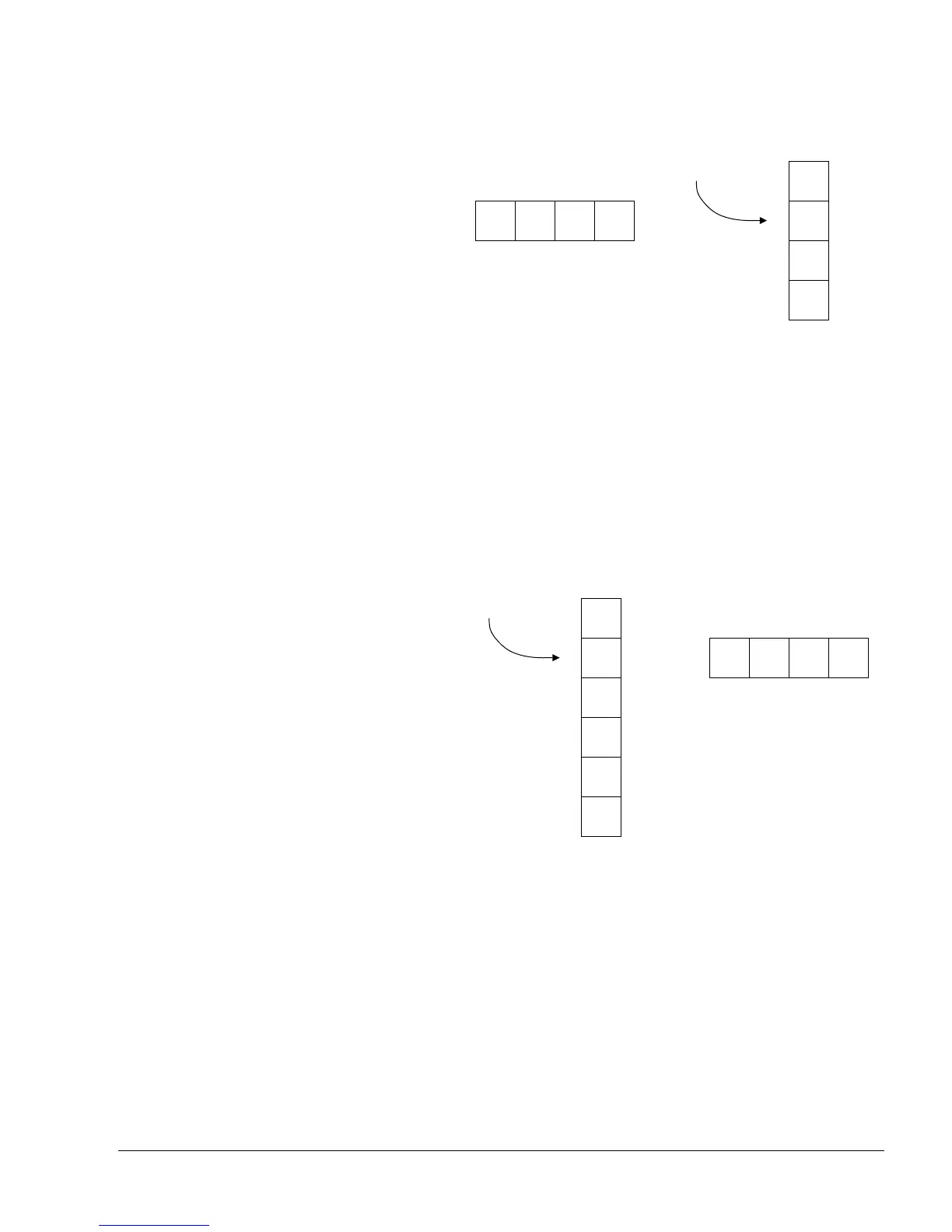

Figure 4-9 Store halfword, big-endian

If strict alignment fault checking is enabled and Address bit 0 is not zero, then a Data Abort is

generated and the MMU returns a Misaligned fault in the Fault Status Register.

4.3.10 Load word, little-endian

The addressed byte-quad is loaded from memory into the 32-bit general-purpose register so that

the least-significant addressed byte in memory appears in bits [7:0] of the ARM register, as

Figure 4-10 shows.

Figure 4-10 Load word, little-endian

If strict alignment fault checking is enabled and Address bits [1:0] are not zero, then a Data

Abort is generated and the MMU returns a Misaligned fault in the Fault Status Register.

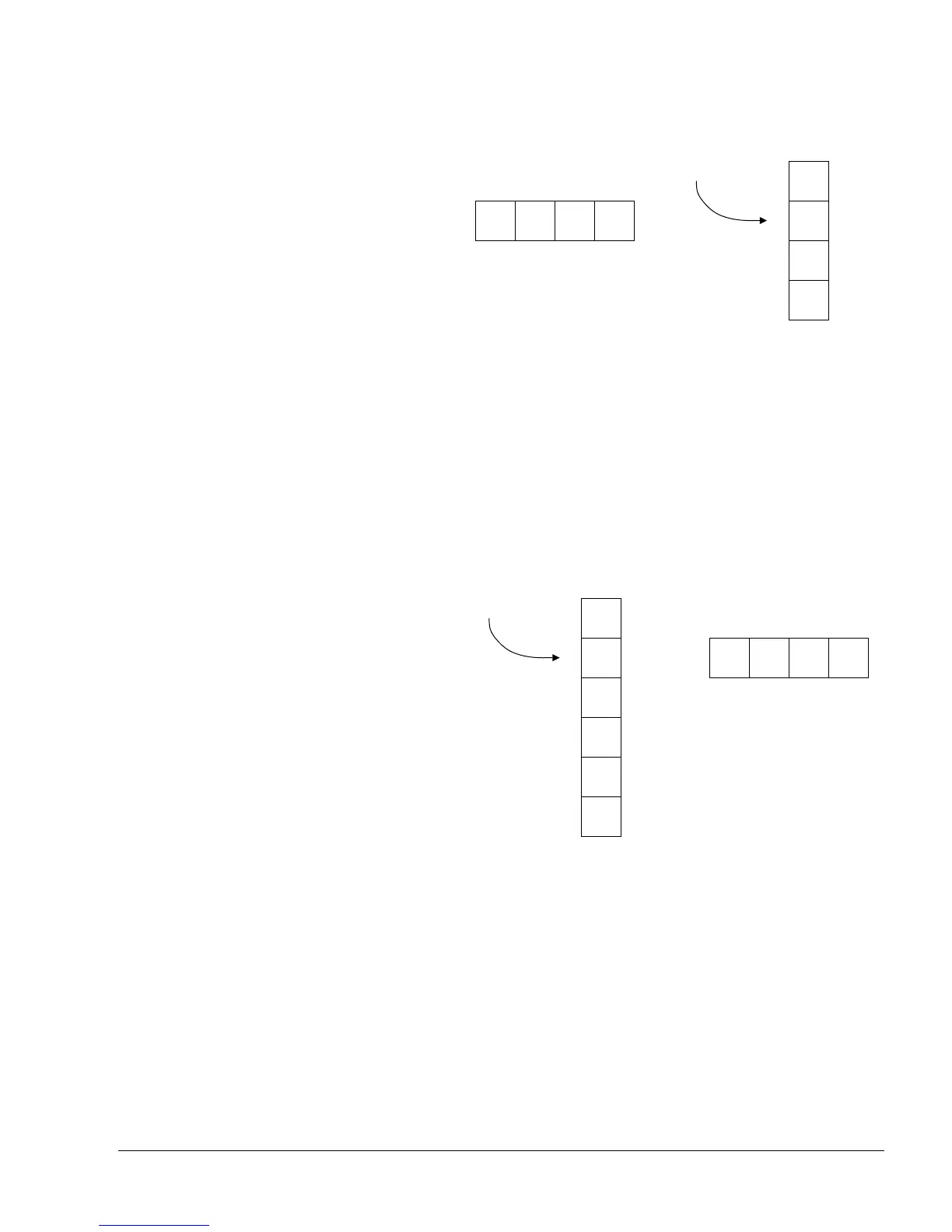

4.3.11 Load word, big-endian

The addressed byte-quad is loaded from memory into the 32-bit general-purpose register so that

the most significant addressed byte in memory appears in bits [31:24] of the ARM register, as

Figure 4-11 on page 4-11 shows.

Register

31 23 15 7 0

x x B0 B1

B1

B0

Memory

Address

A[31:0]

70

+1 lsbyte

msbyte

b1

b0

Memory Register

31 23 15 7 0

Address

A[31:0]

70

b3 b2 b1 b0

b2

+1

msbyte

lsbyte

b3

+2

+3

Loading...

Loading...