VFP Programmer’s Model

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 20-8

ID012310 Non-Confidential, Unrestricted Access

20.3 ARMv5TE coprocessor extensions

This section describes the syntax and usage of the four ARMv5TE architecture coprocessor

extension instructions:

• FMDRR

• FMRRD on page 20-9

• FMSRR on page 20-10

• FMRRS on page 20-11.

Note

These instructions are implementations of the MCRR and MRRC instructions, that Section A10

of the ARM Architecture Reference Manual describes.

20.3.1 FMDRR

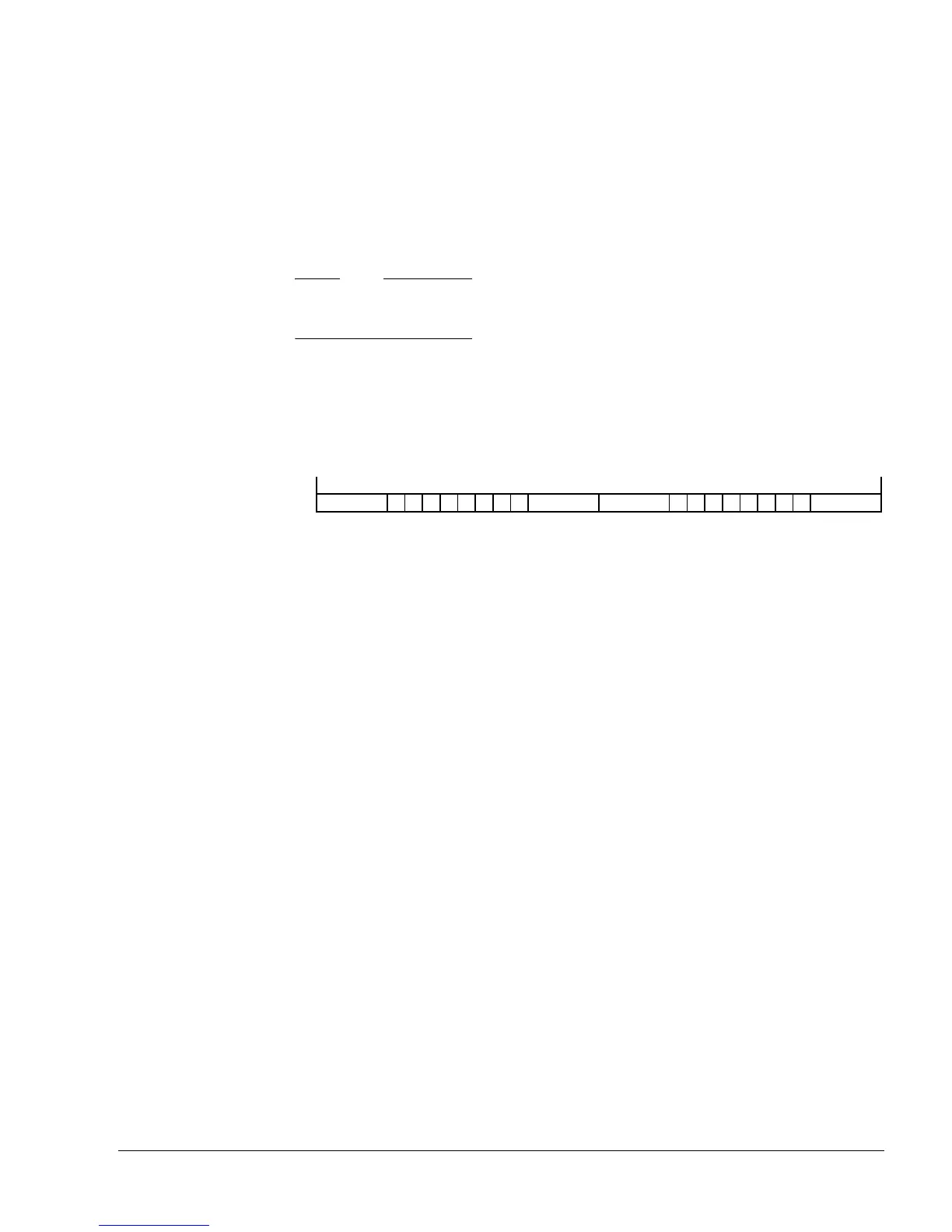

FMDRR transfers data from two ARM11 registers to a VFP11 double-precision register. The

ARM11 registers do not have to be contiguous. Figure 20-1 shows the format of the FMDRR

instruction.

Figure 20-1 FMDRR instruction format

Syntax

FMDRR {<cond>} <Dm>, <Rd>, <Rn>

where:

<cond>

Is the condition under which the instruction is executed. If <cond> is omitted, the

AL, always, condition is used.

<Dm>

Specifies the destination double-precision VFP11 coprocessor register.

<Rd>

Specifies the source ARM11 register for the lower 32 bits of the operand.

<Rn>

Specifies the source ARM11 register for the upper 32 bits of the operand.

Architecture version

D variants only

Exceptions

None

Operation

if ConditionPassed(cond) then

Dm[upper half] = Rn

Dm[lower half] = Rd

1 1 0 0 0 1 0 0 Rn Rd 1 0 1 1 0 0 0 1 Dm

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond

Loading...

Loading...