Cycle Timings and Interlock Behavior

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 16-23

ID012310 Non-Confidential, Unrestricted Access

16.13 RFE and SRS instructions

This section describes the cycle timing for the RFE and SRS instructions.

These instructions return from an exception and save exception return state respectively. The

RFE instruction always requires two memory cycles. It first loads the SPSR value from the

stack, and then the return address. The SRS instruction takes one or two memory cycles

depending on double-word alignment first address location.

In all cases the base register is an Early Reg, and requires an extra cycle of result latency to

provide its value.

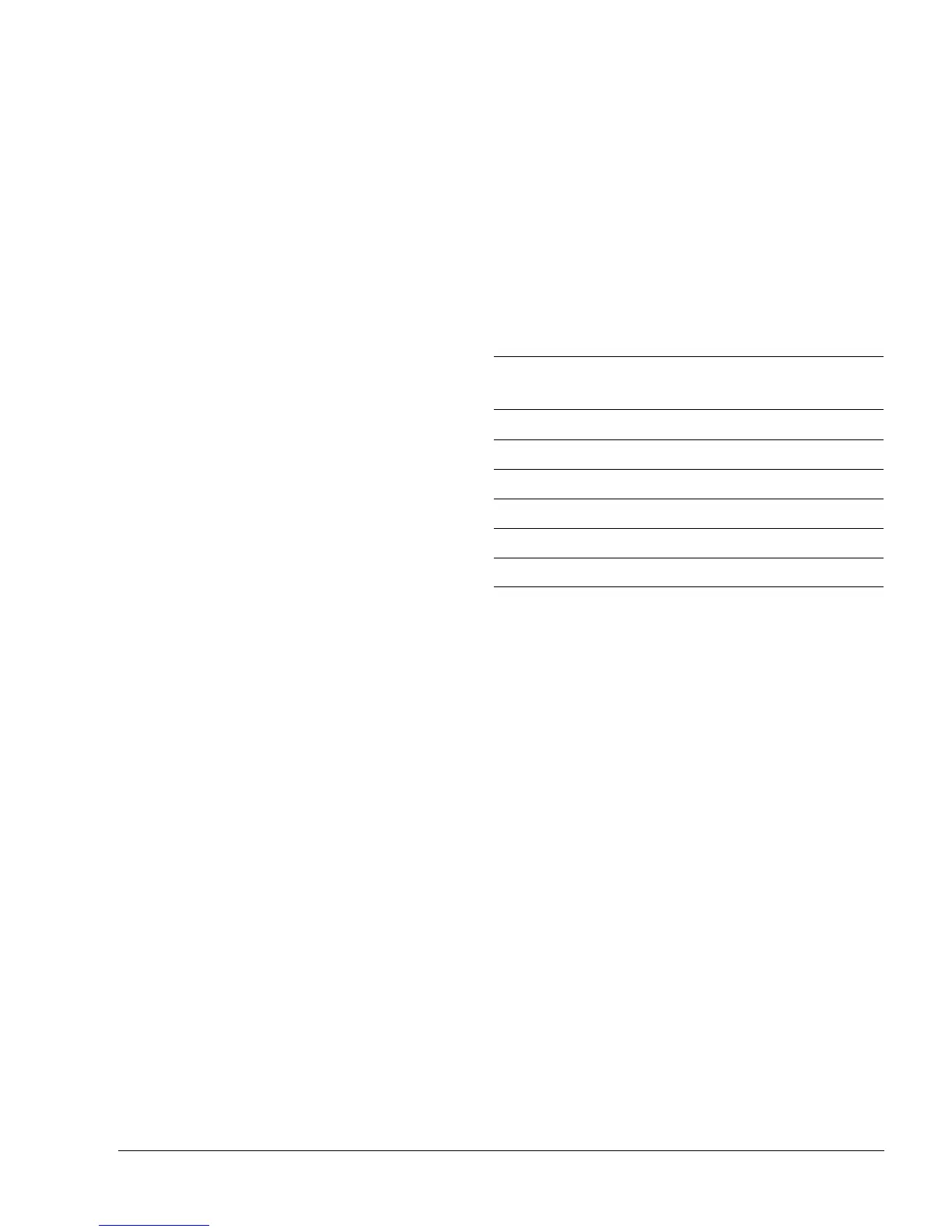

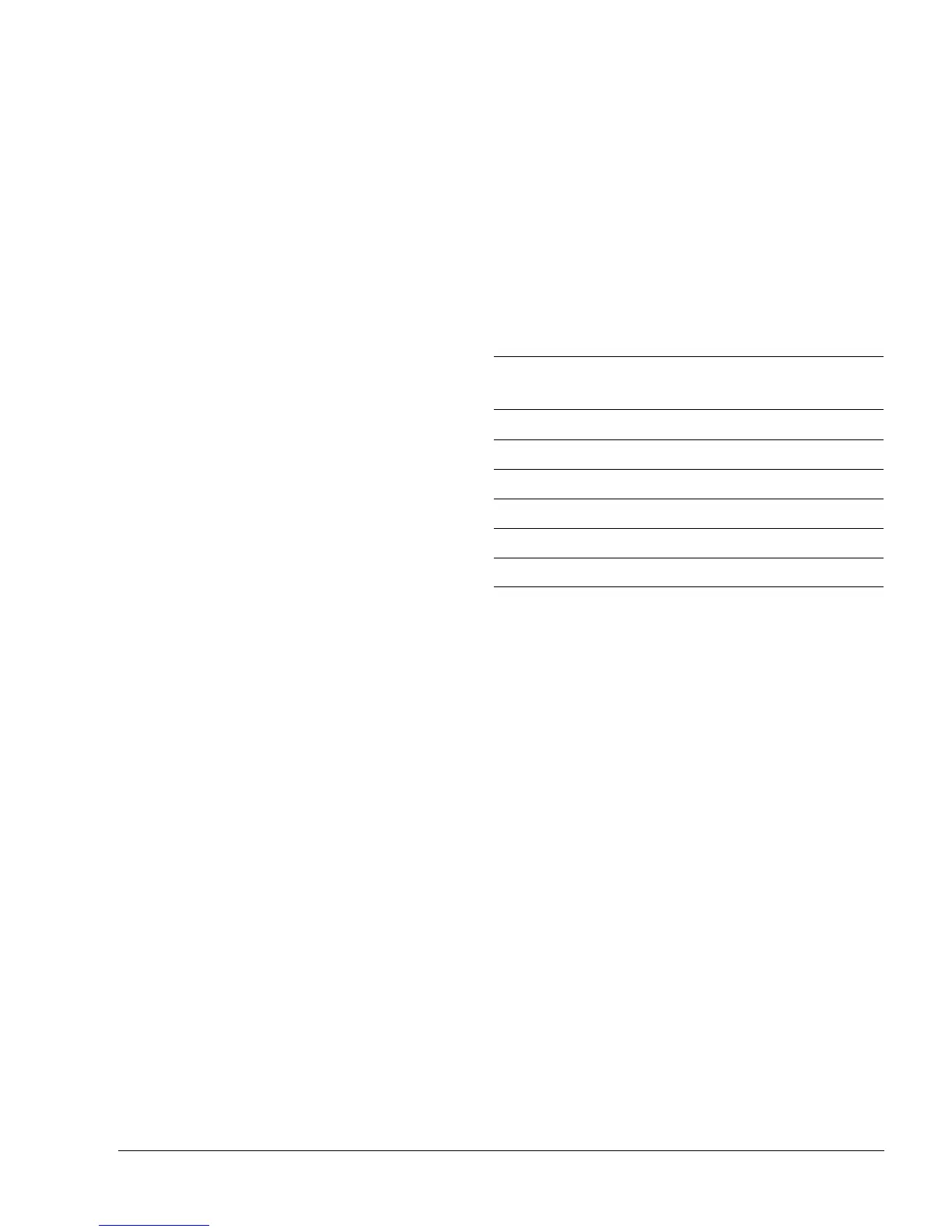

Table 16-20 lists the cycle timing behavior for RFE and SRS instructions.

Table 16-20 RFE and SRS instructions cycle timing behavior

Example Instruction

Cycle

s

Memory Cycles

Address double-word aligned

RFEIA <Rn>

92

SRSIA #<mode>

11

Address not double-word aligned

RFEIA <Rn>

92

SRSIA #<mode>

12

Loading...

Loading...