The VFP Register File

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 19-4

ID012310 Non-Confidential, Unrestricted Access

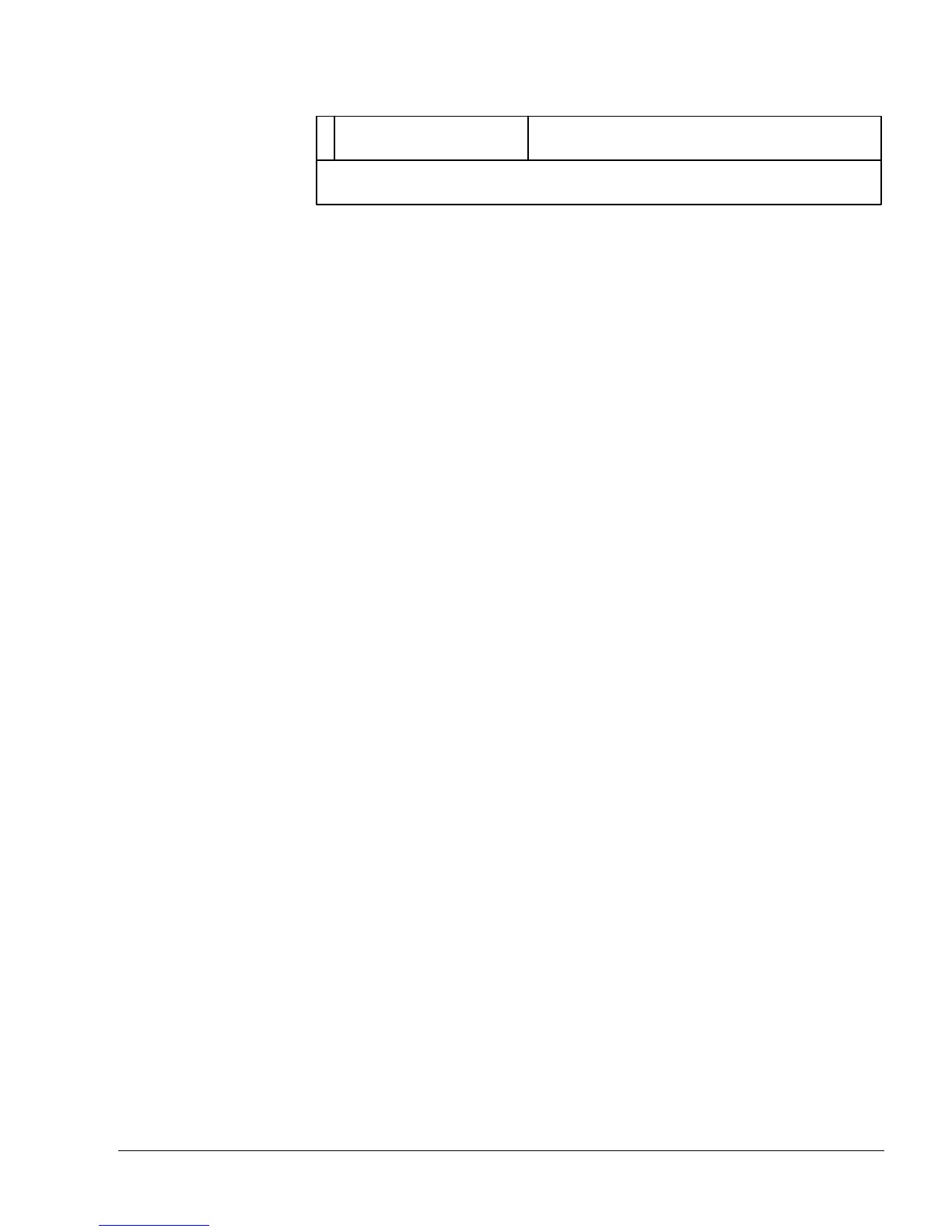

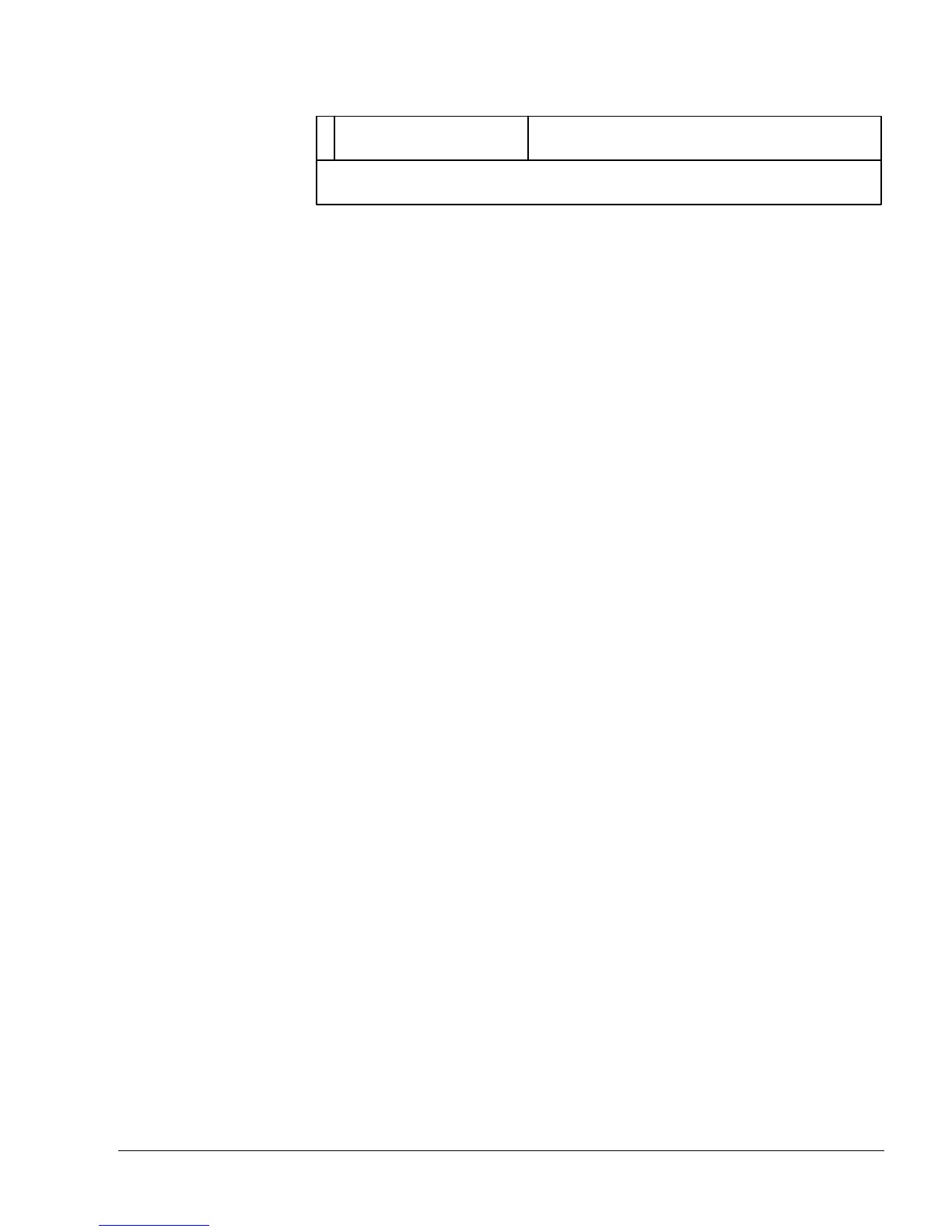

Figure 19-2 Double-precision data format

The MSW contains:

• the sign bit, bit [31]

• the exponent, bits [30:20]

• the upper 20 bits of the fraction, bits [19:0].

The LSW contains the lower 32 bits of the fraction.

The IEEE 754 standard defines the double-precision data format used in the VFP11

coprocessor. See the IEEE 754 standard for details about exponent bias, special formats, and

numerical ranges.

31

Exponent Fraction, upper 20 bitsS

30 20 19 0

Fraction, lower 32 bits

Double-precision

MSW

Double-precision

LSW

Loading...

Loading...